સમાંતર કમ્પ્યુટિંગ

સમાંતર કમ્પ્યુટિંગ એ પરિકલન (કમ્પ્યુટેશન)નો પ્રકાર છે જેમાં અનેક ગણતરી એક સાથે કરવામાં આવે છે.[૧] જે એવા સિદ્ધાંત પર કામ કરે છે કે મોટા કૂટપ્રશ્નોને ઘણી વાર નાના કૂટપ્રશ્નોમાં વિભાજિત કરી શકાય છે, જેને પછી સંગામી રીતે (“સમાંતરે”) ઉકેલી શકાય છે. સમાંતર કમ્પ્યુટિંગના કેટલાક વિવિધ પ્રકાર છેઃ બિટ-સ્તર, સૂચના સ્તર, ડેટા અને ટાસ્ક પેરલલિઝમ. પેરલલિઝમ ઘણા વર્ષથી લાગુ કરવામાં આવેલ છે, ખાસ કરીને ઉચ્ચ પ્રદર્શન ધરાવતા પરિકલનમાં, પરંતુ ભૌતિક મર્યાદાઓના કારણે ફ્રિકવન્સી સ્કેલિંગ અટકતું હોવાથી તેમાં તાજેતરમાં રસ વધ્યો છે.[૨] કમ્પ્યુટર્સ દ્વારા વીજ વપરાશ (અને તેના પરિણામે ગરમીની પેદાશ) તાજેતરમાં ચિંતાનું કારણ છે,[૩] તેથી સમાંતર કમ્પ્યુટિંગ કમ્પ્યુટર આર્કિટેક્ચરમાં, ખાસ કરીને મલ્ટિકોર પ્રોસેસર્સના સ્વરૂપમાં પ્રભાવશાળી ફેરફાર બન્યો છે.[૪]

સમાંતર કમ્પ્યુટર્સને હાર્ડવેર જે સ્તરે પેરલલિઝમને ટેકો આપે તે મુજબ સામાન્ય રીતે વર્ગીકૃત કરવામાં આવે છે- જેમાં એક મશીનમાં મલ્ટીપલ પ્રોસેસિંગ તત્વો ધરાવતા મલ્ટી-કોર અને મલ્ટિ-પ્રોસેસર કમ્પ્યુટર્સને ટેકો મળે છે જ્યારે ક્લસ્ટર્સ, એમપીપી (MPP) અને ગ્રીડ સમાન ટાસ્ક પર કામ કરવા માટે મલ્ટિપલ કમ્પ્યુટર્સનો ઉપયોગ કરે છે. ચોક્કસ કામની ઝડપ વધારવા માટે ઘણી વાર પરંપરાગત પ્રોસેસર્સ સાથે વિશેષ સમાંતર કમ્પ્યુટિંગ આર્કિટેક્ચરનો ઉપયોગ કરવામાં આવે છે.

સિક્વન્સિયલ પ્રોગ્રામ્સની સરખામણીમાં સમાંતર કમ્પ્યુટિંગ પ્રોગ્રામ્સને લખવાનું વધુ મુશ્કેલ હોય છે[૫] કારણ કે સમાંતર હોવાના કારણે સંભવિત સોફ્ટવેર બગ્સના નવા વર્ગ રજૂ થાય છે જેમાંથી રેસની સ્થિતિ સૌથી વધુ સામાન્ય છે. સંદેશાવ્યવહાર અને વિવિધ સબટાસ્ક વચ્ચે સિન્ક્રોનાઇઝેશન સારા પ્રોગ્રામ કામગીરી માટે સૌથી મોટા પડકારો પૈકી એક છે.

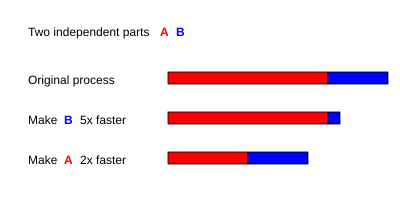

સમાંતર પ્રક્રિયાના પરિણામે પ્રોગ્રામમાં ગતિમાં વધારો એમડલના નિયમ તરીકે ઓળખાય છે.

પૃષ્ઠભૂમિ

[ફેરફાર કરો]પરંપરાગત રીતે કમ્પ્યુટર સોફ્ટવેર શ્રેણીબદ્ધ પરિકલન માટે લખવામાં આવેલ હોય છે. કૂટપ્રશ્નોના ઉકેલ માટે એક એલ્ગોરિધમ રચવામાં આવે છે અને સૂચનાઓના શ્રેણીબદ્ધ પ્રવાહ તરીકે લાગુ પાડવામાં આવે છે. આ સૂચનાઓ એક કમ્પ્યુટરના સેન્ટ્રલ પ્રોસેસિંગ યુનિટ પર અમલી કરવામાં આવે છે. એક સમયે માત્ર એક સૂચનાનું પાલન થાય છે. તે સમાપ્ત થયા બાદ બીજી સૂચના પર કામ થાય છે.[૬]

બીજી તરફ સમાંતર કમ્પ્યુટિંગમાં કૂટપ્રશ્નના ઉકેલ માટે એકથી વધુ પ્રોસેસિંગ ઘટકોનો એક સાથે ઉપયોગ થાય છે. તેમાં કૂટપ્રશ્નને અનેક સ્વતંત્ર ભાગોમાં વિભાજિત કરવામાં આવે છે જેથી દરેક પ્રોસેસિંગ ઘટક બીજાની સાથે એક સાથે પોતાના ભાગના એલ્ગોરિધમનો અમલ કરી શકે. પ્રોસેસિંગ ઘટકો વિવિધતા ધરાવતા હોઇ શકે અને તેમાં અનેકવિધ પ્રોસેસર્સ, વિવિધ નેટવર્ક્ડ કમ્પ્યુટર્સ, સ્પેશિયલાઇઝ્ડ હાર્ડવેર સાથેના સ્રોતો અથવા ઉપરના કોઇ પણના સંયોજનનો સમાવેશ થઈ શકે.[૬]

1980ના દાયકાના મધ્યથી 2004 સુધી કમ્પ્યુટરની કામગીરીમાં સુધારા માટે ફ્રિકવન્સી સ્કેલિંગ પ્રભાવક કારણ હતું. પ્રોગ્રામનો રનટાઇમ સૂચનાઓની સંખ્યાના પ્રતિ સૂચના સરેરાશ સમય સાથેના ગુણાકારની સમાન હોય છે. બાકીના બધાને અચળ રાખવાથી અને ક્લોક આવૃત્તિ વધારવાથી સૂચનાના અમલીકરણ માટેનો સરેરાશ સમય ઘટે છે. આમ આવૃત્તિમાં વધારો તમામ કમ્પ્યુટેશન બાઉન્ડેડ પ્રોગ્રામ્સ માટે રનટાઇમમાં ઘટાડો કરે છે.[૭]

જોકે, ચીપ દ્વારા શક્તિનો વપરાશ P = C × V2 × F સમીકરણને અનુસરે છે જ્યાં પી (P) એટલે પાવર (શક્તિ), સી (C) એટલે પ્રતિ ક્લોક ચક્રમાં સ્વીચ થતી કેપેસિટન્સ (જેના ઇનપુટમાં ફેરફાર થયો છે તે ટ્રાન્ઝિસ્ટર્સની સંખ્યાના પ્રમાણમાં), વી (V) એટલે વોલ્ટેજ અને એફ (F) એટલે પ્રોસેસર ફ્રિકવન્સી (પ્રતિ સેકન્ડ ચક્ર) છે.[૮] આવૃત્તિમાં વધારો કરવાથી પ્રોસેસરમાં ઉપયોગમાં લેવાતી શક્તિના પ્રમાણમાં વધારો થાય છે. પ્રોસેસિંગ શક્તિની ખપતમાં વધારાથી ઇન્ટેલે મે 2004માં તેના તેજસ અને જેહોક પ્રોસેસરને અંતે રદ કરવામાં આવ્યા હતા જેને સામાન્ય રીતે પ્રભાવક કમ્પ્યુટર આર્કિટેક્ચર ફેરફારમાં ફ્રિકવન્સી સ્કેલિંગના અંત તરીકે ટાંકવામાં આવે છે.[૯]

મૂરેનો નિયમ પ્રયોગાત્મક નિરિક્ષણ છે કે માઇક્રોપ્રોસેસરમાં ટ્રાન્ઝિસ્ટર ઘનતા દર 18થી 24 મહિને બમણી થાય છે.[૧૦] શક્તિના વપરાશના મુદ્દા અને તેના છેડા વિશે વારંવાર આગાહીઓ હોવા છતાં મૂરેનો નિયમ હજુ અમલમાં છે. ફ્રિકવન્સી સ્કેલિંગના અંત સાથે આ વધારાના ટ્રાન્ઝિસ્ટર્સ (જેનો ઉપયોગ ફ્રિકવન્સી સ્કેલિંગ માટે થતો નથી)નો ઉપયોગ સમાંતર કમ્પ્યુટિંગ માટે વધારાના હાર્ડવેરના ઉમેરા માટે થઈ શકે છે.

એમડલનો નિયમ અને ગુસ્ટેફ્સનનો નિયમ

[ફેરફાર કરો]

શ્રેષ્ઠ રીતે જોવામાં આવે તો સમાંતર પ્રક્રિયાના કારણે ગતિમાં વધારો એક નિશ્ચિત ગુણાંકમાં જોવા મળશે જેમાં પ્રોસેસિંગ કરતા ઘટકોની સંખ્યા બમણી કરવાથી રનટાઇમ અડધો થશે અને તેને ફરી એક વાર બમણાં કરવાથી ફરી તેના રનટાઇમમાં ઘટાડો થશે. કે બહુ ઓછા સમાંતર એલ્ગોરિધમ્સ મહત્તમ સ્પીડ અપ પ્રાપ્ત કરે છે. તેમાંથી મોટા ભાગના નાની સંખ્યામાં પ્રોસેસિંગ ભાગો માટે લગભગ લિનીયર સ્પીડ અપ ધરાવે છે. જેનાથી મોટી સંખ્યામાં પ્રોસેસિંગ ઘટકો માટે અચળ મૂલ્યમાં રૂપાંતરિત થાય છે.

સમાંતર કમ્પ્યુટિંગ પ્લેટફોર્મ પર સંભવિત સ્પીડ-અપ એમડલના નિયમ પર આધારિત હોય છે જે અસલમાં 1960ના દાયકામાં જીન એમડલ દ્વારા રચવામાં આવ્યો હતો.[૧૧] તેમાં જણાવાયું છે કે સમાંતર કરી ન શકાય તેવા પ્રોગ્રામના નાના હિસ્સાથી સમાંતર પ્રક્રિયામાંથી સ્પીડ-અપમાં મર્યાદા આવશે. કોઇ મોટી ગાણિતિક કે એન્જિનિયરિંગ કૂટપ્રશ્નમાં દેખીતી રીતે જ કેટલાક સમાંતર કરી શકાય તેવા ભાગ અને કેટલાક સમાંતર ન કરી શકાય તેવા ભાગ (ક્રમિક) હશે. આ સંબંધ નીચેના સમીકરણ દ્વારા સમજાવવામાં આવે છે.

જેમાં S (એસ) પ્રોગ્રામનો સ્પીડ-અપ (અસલ ક્રમિક રનટાઇમના પરિબળ તરીકે) અને P (પી) સમાંતર કરી શકાય તે હિસ્સો છે. પ્રોગ્રામનો ક્રમિક હિસ્સો જો રનટાઇમના 10% હોય તો આપણે 10×થી વધારે સ્પીડ-અપ મેળવી શકતા નથી, ભલે તેમાં ગમે તેટલા પ્રોસેસર્સ ઉમેરવામાં આવ્યા હોય. તેના કારણે વધારે સમાંતર એક્ઝિક્યુશન એકમ ઉમેરવાની ઉપલી ટોચમર્યાદા લાગુ થાય છે. “ક્રમિક મર્યાદાઓના કારણે ટાસ્કને જ્યારે વિભાજિત કરી ન શકાય ત્યારે વધુ પ્રયાસો લાગુ પાડવાની કોઇ અસર શિડ્યુલ પર થતી નથી. બાળકના જન્મને નવ મહિનાનો સમય લાગે છે, ભલે તે પ્રક્રિયામાં ગમે તેટલી મહિલાઓ સામેલ થાય.”[૧૨]

ગુસ્ટેફ્સનનો નિયમ ગણનનો વધુ એક નિયમ છે, જે એમડલના નિયમ સાથે નિકટતાથી સંકળાયેલ છે. તેને નીચે મુજબ ફોર્મ્યુલામાં ગોઠવી શકાય,

જેમાં P (પી) એ પ્રોસેસર્સની સંખ્યા, S (એસ) સ્પીડ અપ અને α (એ) પ્રક્રિયાનો બિનસમાંતર ભાગ છે.[૧૩] એમડલનો નિયમ એક નિશ્ચિત કૂટપ્રશ્નનું કદ ધરાવે છે અને ક્રમિક હિસ્સો પ્રોસેસર્સની સંખ્યાથી સ્વતંત્ર છે જ્યારે ગુસ્ટેફ્સનનો નિયમ આ ધારણાઓને ધ્યાનમાં લેતો નથી.

ડિપેન્ડન્સી

[ફેરફાર કરો]સમાંતર એલ્ગોરિધમ્સ લાગુ પાડવામાં ડેટા ડિપેન્ડન્સીની સમજણ મૂળભૂત છે. ડિપેન્ડન્ટ ગણતરીઓ (ક્રિટિકલ પથ તરીકે ઓળખાતી)ની સૌથી લાંબી શ્રૃંખલા કરતા વધુ ઝડપથી કોઇ પ્રોગ્રામ ચાલી શકે નહીં, કારણ કે શ્રૃંખલામાં પૂર્વ ગણતરી પર આધારિત ગણતરીઓ ક્રમ પ્રમાણે લાગુ થવી જોઇએ. જોકે, મોટા ભાગના એલ્ગોરિધમ્સમાં માત્ર ડિપેન્ડન્ટ ગણતરીઓની લાંબી શ્રૃંખલા નથી હોતી, સમાંતરમાં સ્વતંત્ર ગણતરીઓ લાગુ પાડવા માટે સામાન્ય રીતે તક હોય છે.

Pi અને Pj બે પ્રોગ્રામ ફ્રેગમેન્ટ્સ છે. બર્નસ્ટેઇનની શરત[૧૪] જણાવે છે કે ક્યારે આ બે સ્વતંત્ર હોય અને સમાંતર રીતે લાગુ કરી શકાય. P i માટે I i ને ઇનપુટ વેરિયેબલ્સ અને O i ને આઉટપુટ વેરિયેબલ્સ હોય અને તેવી રીતે P j માટે હોય છે. P i અને P j સ્વતંત્ર હોય છે જો તે નીચેની સ્થિતિને સંતોષી શકે.

પ્રથમ શરતનો ભંગ ફ્લો ડિપેન્ડન્સી રજૂ કરે છે, જે પ્રથમ નિવેદન સાથે સંબંધિત છે જે બીજા નિવેદન દ્વારા સર્જાતા નિવેદનનું પરિણામ રજૂ કરે છે. બીજા નિવેદનમાં એક એન્ટી-ડિપેન્ડન્સી રજૂ થાય છે જ્યારે બીજું નિવેદન (P j ) પ્રથમ મંતવ્ય (P i ) માટે જરૂરી વેરિયેબલ ઓવરરાઇટ કરશે. ત્રીજી અને અંતિમ શરત એક આઉટપુટ ડિપેન્ડન્સી રજૂ કરે છે. જ્યારે બે નિવેદન એકજ સ્થળ પર લખાય છે ત્યારે અંતિમ પરિણામ તાર્કીક રીતે છેલ્લે લાગુ થયેલા નિવેદનમાંથી મળવું જોઇએ.[૧૫]

નીચેના વિધેય (ફંક્શન) અંગે વિચારણા કરો જે વિવિધ પ્રકારની ડિપેન્ડન્સી દર્શાવે છેઃ

1: ફંકશન ડેપ(a, b) 2: c := a·b 3: d := 2·c 4: એન્ડ ફંક્શન

ડેપ (a, b)માં ઓપરેશન 3ને ઓપરેશન 2 અગાઉ (અથવા સમાંતરમાં) લાગુ કરી શકાય નહીં, કારણ કે ઓપરેશન 3માં ઓપરેશન 2ના પરિણામનો ઉપયોગ થાય છે. તે શરત 1નો ભંગ કરે છે તેથી ફ્લો ડિપેન્ડન્સી રજૂ કરે છે.

1: ફંકશન નોડેપ (a, b) 2: c := a·b 3: d := 2·b 4: e := a+b 5: એન્ડ ફંક્શન

આ ઉદાહરણમાં સૂચનાઓ વચ્ચે કોઇ ડિપેન્ડન્સી નથી, તેથી તે તમામ સમાંતર ચાલુ કરી શકાય છે.

બર્નસ્ટેઇનની શરત વિવિધ પ્રક્રિયા વચ્ચે મેમરીની હિસ્સેદારી (શેરિંગ)ની છૂટ આપતી નથી. તેથી એક્સેસ વચ્ચે ક્રમ લાગુ પાડવાની કોઇ પદ્ધતિ આવશ્યક છે, જેમ કે સીમાફોર્સ, અવરોધો (બેરિયર્સ) અથવા અન્ય કોઇ લયબદ્ધ (સિન્ક્રોનાઇઝેશન) પદ્ધતિ.

રેસ શરતો, મ્યુચ્યુઅલ એક્સક્લુઝન, સિન્ક્રોનાઇઝેશન અને સમાંતર ગતિરોધ

[ફેરફાર કરો]સમાંતર પ્રોગ્રામમાં સબટાસ્ક (પેટાકાર્ય)ને ઘણી વાર થ્રેડ્સ તરીકે ઓળખવામાં આવે છે. કેટલાક સમાંતર કમ્પ્યુટર આર્કિટેક્ચર નાના, હળવા વજનના થ્રેડ્સના સ્વરૂપનો ઉપયોગ કરે છે જે ફાઇબર તરીકે ઓળખાય છે, જ્યારે અન્ય વધુ મોટા વર્ઝન પ્રોસેસ તરીકે ઓળખાય છે. જોકે “થ્રેડ્સ” સામાન્ય રીતે સબટાસ્કના જેનરિક (સામાન્ય) અર્થ તરીકે વાપરવામાં આવે છે. થ્રેડ્સમાં ઘણી વાર કેટલાક વેરિયેબલને અપડેટ કરવાની જરૂર પડશે જેને તેમની વચ્ચે હિસ્સેદારી કરવામાં આવે છે. બે પ્રોગ્રામ્સ વચ્ચેની સૂચના અન્ય ક્રમમાં ગુંથાયેલ હોઇ શકે છે. ઉદાહરણ તરીકે નીચેના પ્રોગ્રામને ધ્યાનમાં લોઃ

| થ્રેડ A | થ્રેડ B |

| 1A: વેરિયેબલ V વાંચો | 1B: વેરિયેબલ V વાંચો |

| 2A: વેરિયેબલ Vમાં 1 ઉમેરો | 2B: વેરિયેબલ Vમાં 1 ઉમેરો |

| 3A વેરિયેબલ V પર ફરી લખો | 3B: વેરિયેબલ V પર ફરી લખો |

જો સૂચના 1Bને 1A અને 3A વચ્ચે લાગુ પાડવામાં આવે અને જો સૂચના 1A ને 1B અને 3B વચ્ચે લાગુ પાડવામાં આવે તો પ્રોગ્રામ સાચા ડેટા રજૂ કરશે. તેને રેસ કંડિશન (શરત) તરીકે ઓળખવામાં આવે છે. પ્રોગ્રામરે મ્યુચ્યુઅલ એક્સક્લુઝન પૂરું પાડવા માટે લોકનો ફરજિયાત ઉપયોગ કરવો પડે. લોક એ પ્રોગ્રામિંગ લેંગ્વેજ રચના છે જે એક થ્રેડને વેરિયેબલનું નિયંત્રણ મેળવવા અને જ્યાં સુધી તે વેરિયેબલ ખોલવામાં ન આવે ત્યાં સુધી બીજા થ્રેડને તેને વાંચતા કે લખતા અટકાવે છે. લોક ધરાવતું થ્રેડ તેનું ક્રિટિકલ સેક્સન (પ્રોગ્રામનો હિસ્સો જેમાં કેટલાક વેરિયેબલ માટે સંપૂર્ણ એક્સેસની જરૂર પડે છે) લાગુ પાડવા અને અને તે પૂર્ણ થઇ જાય ત્યારે ડેટાને મુક્ત કરવા માટે સ્વતંત્ર છે. તેથી ખરા પ્રોગ્રામ અમલીકરણની ખાતરી આપવા માટે ઉપરના પ્રોગ્રામને લોકના ઉપયોગ માટે ફરી લખી શકાય છે:

| થ્રેડ A | થ્રેડ B |

| 1A: લોક વેરિયેબલ V | 1B: લોક વેરિયેબલ V |

| 2A: રીડ વેરિયેબલ V | 2B: રીડ વેરિયેબલ V |

| 3A: વેરિયેબલ Vમાં 1 ઉમેરો | 3B: વેરિયેબલ Vમાં 1 ઉમેરો |

| 4A વેરિયેબલ Vમાં ફરી લખો | 4B: વેરિયેબલ Vમાં ફરી લખો |

| 5A: વેરિયેબલ Vને અનલોક કરો | 5B: વેરિયેબલ Vને અનલોક કરો |

એક થ્રેડ સફળ રીતે વેરિયેબલ Vને લોક કરશે જ્યારે બીજું થ્રેડ લોક્ડ આઉટ થશે. તેથી vને જ્યાં સુધી અનલોક (ખોલવામાં) કરવામાં ન આવે ત્યાં સુધી આગળ નહીં વધી શકે. તેના કારણે પ્રોગ્રામ યોગ્ય રીતે લાગુ થવાની ખાતરી મળે છે. યોગ્ય પ્રોગ્રામ અમલીકરણ માટે લોક જરૂરી છે, પરંતુ તેનાથી પ્રોગ્રામની ઝડપમાં ઘણો ઘટાડો થઇ શકે છે.

નોન-એટોમિક લોક્સનો ઉપયોગ કરીને એકથી વધુ વેરિયેબલને લોક કરવાથી પ્રોગ્રામ ડેડલોકની સંભાવના રજૂ થાય છે. એટોમિક લોકમાં એક સાથે એકથી વધુ વેરિયેબલને લોક કરવામાં આવે છે. તે તેમાના તમામને લોક ન કરી શકે તો તે તેમાંથી કોઇને લોક કરી શકશે નહીં. જો બે થ્રેડને નોન એટોમિક લોકનો ઉપયોગ કરીને સમાન બે વેરિયેબલ્સને લોક કરવાની જરૂર પડે તો, શક્ય છે કે એક થ્રેડ તેમાંના એકને લોક કરશે અને બીજું થ્રેડ બીજા વેરિયેબલને લોક કરશે. આવા કિસ્સામાં કોઇ થ્રેડ સંપૂર્ણ થઇ શકે નહીં અને પરિણામે ડેડલોક સર્જાશે.

ઘણા સમાંતર પ્રોગ્રામમાં સબટાસ્ક સિન્ક્રોનાઇઝેશનમાં કામ કરે તેવી જરૂરિયાત પેદા થાય છે. તેના માટે બેરિયરનો ઉપયોગ કરવો પડે છે. બેરિયર સામાન્ય રીતે સોફ્ટવેર લોકનો ઉપયોગ કરીને લાગુ કરવામાં આવે છે. લોક ફ્રી અને વેઇટ ફ્રી એલ્ગોરિધમ્સ તરીકે ઓળખાતો એલ્ગોરિધમ્સનો એક પ્રકાર સંયુક્ત રીતે લોક્સ અને વેરિયેબલ્સનો ઉપયોગ ટાળે છે. જોકે, આ વલણ સામાન્ય રીતે લાગુ પાડવું મુશ્કેલ છે અને યોગ્ય રીતે ડિઝાઇન કરવામાં આવેલા ડેટા માળખાની જરૂર પડે છે.

તમામ સમાંતર પ્રક્રિયાથી ગતિમાં વધારો થતો નથી. સામાન્ય રીતે એક કામ વધુને વધુ થ્રેડમાં વિભાજિત કરવામાં આવે ત્યારે આ થ્રેડ તેમના સમયનો વધુને વધુ હિસ્સો એક બીજા સાથે સંપર્ક સાધવામાં ખર્ચે છે. અંતે કમ્યુનિકેશનને ઓવરહેડ કૂટપ્રશ્ન ઉકેલવા માટે ખર્ચાયેલા સમય પર પ્રભાવિત થાય છે અને વધુ સમાંતરણથી (જેમાં કામના બોજને વધુને વધુ થ્રેડમાં વિભાજિત કરવામાં આવે છે) કામ પૂર્ણ કરવા માટે લાગતો સમય ઘટવાના બદલે વધે છે. તેને સમાંતર સ્લોડાઉન તરીકે ઓળખવામાં આવે છે.

ફાઇન-ગ્રેઇન્ડ, કોઅર્સ ગ્રેઇન્ડ અને એમ્બેરેસિંગ પેરલલિઝમ

[ફેરફાર કરો]એપ્લિકેશન્સને ઘણી વાર તેમના સબટાસ્ક (પેટાકાર્ય)ને સિન્ક્રોનાઇઝ કરવાની જરૂર પડે છે અથવા એક બીજા સાથે કોમ્યુનિકેટ થાય છે તેના આધારે વિભાજિત કરવામાં આવે છે. કોઇ એપ્લિકેશનમાં સબટાસ્કે દર સેકન્ડે અનેક વાર કોમ્યુનિકેટ કરવાનું હોય તો તે ફાઇન-ગ્રેઇન્ડ સમાંતરણ રજૂ કરે છે, જો તે દર સેકન્ડે અનેક વાર કોમ્યુનિકેટ ન કરે તો તે કોઅર્સ-ગ્રેઇન્ડ સમાંતરણ રજૂ કરે છે અને ભાગ્યે જ કોમ્યુનિકેટ કરે અથવા ક્યારેય કોમ્યુનિકેટ ન કરે તો એમ્બેરેસિંગલી સમાંતર હોય છે. એમ્બેરેસિંગ સમાંતર એપ્લિકેશન્સને સમાંતરમાં સૌથી સરળ માનવામાં આવે છે.

સાતત્યતાની મોડલ્સ

[ફેરફાર કરો]સમાંતર પ્રોગ્રામિંગ લેંગ્વેજ અને સમાંતર કમ્પ્યુટર્સમાં સાતત્યનું મોડલ (મેમરી મોડલ તરીકે પણ ઓળખાય છે) હોવું જરૂરી છે. કમ્પ્યુટર મેમરી પર પ્રક્રિયા કઇ રીતે થાય છે અને કઇ રીતે પરિણામ પેદા થાય છે તેના નિયમ સાતત્યના મોડલ પરથી નક્કી થાય છે.

પ્રથમ સાતત્યસભર મોડેલો પૈકી એક લેસ્લી લેમ્પોર્ટનું ક્રમિક સાતત્ય મોડલ હતું. ક્રમિક સાતત્ય એક સમાંતર પ્રોગ્રામની પ્રોપર્ટી છે જેમાં તેના સમાંતર અમલીકરણથી ક્રમિક પ્રોગ્રામ જેવા જ પરિણામ રજૂ થાય છે. ખાસ કરીને પ્રોગ્રામને ત્યારે ક્રમિક ગણવામાં આવે છે જ્યારે, “… કોઇ અમલીકરણનું પરિણામ સમાન હોય જાણે તમામ પ્રોસેસર્સના પરિણામો સમાન ક્રમિક ક્રમમાં કરવામાં આવ્યા હોય અને દરેક વ્યક્તિગત પ્રોસેસર્સની કામગીરી તેના પ્રોગ્રામમાં જણાવેલા ક્રમમાં જોવા મળે.”[૧૬] સોફ્ટવેર ટ્રાન્સેક્શનલ મેમરી સમાન પ્રકારનું સાતત્ય મોડલ છે. સોફ્ટવેર ટ્રાન્સેક્શનલ મેમરી ડેટાબેઝ થિયરી પાસેથી એટોમિક ટ્રાન્સેક્શનનો વિચાર મેળવે છે અને મેમરી એક્સેસ પર લાગુ પાડે છે.

ગાણિતિક રીતે આ મોડેલોને વિવિધ પદ્ધતિમાં રજૂ કરી શકાય છે. કાર્લ આદમ પેટ્રીના 1962ની ડોક્ટરલ થિસિસમાં રજૂ થયેલ પેટ્રી નેટ્સ સાતત્ય મોડલના નિયમોને કોડ આપવાનો પ્રથમ પ્રયાસ હતો. ત્યાર બાદ તેના પર ડેટાફ્લો થિયરી બની હતી અને ડેટાફ્લો આર્કિટેક્ચરની રચના ડેટાફ્લો થિયરીને લાગુ કરવા માટે થઈ હતી. 1970ના દાયકાના અંતમાં કેલક્યુલસ ઓફ કોમ્યુનિકેટિંગ સિસ્ટમ્સ અને કોમ્યુનિકેટિંગ સિક્વન્શિયલ પ્રોસેસ જેવી પ્રોસેસ કેલ્ક્યુલીને ડેવલપ કરવામાં આવ્યા જેથી આંતરીક રીતે ગુંથાયેલા હિસ્સાઓની બનેલી સિસ્ટમમાં બીજગણિતીય તર્ક આપી શકાય. પ્રોસેસ કેલ્ક્યુલસ પરિવારના તાજેતરના ઉમેરા જેમ કે π-કેલ્ક્યુલસથી ડાયનેમિક ટોપોલોજિસ અંગે તર્કની ક્ષમતામાં વધારો કર્યો છે. લેમ્પોર્ટ્સના TLA+ જેવા લોજિક્સ (તર્ક) અને ટ્રેસિસ અને એક્ટર ઇવન્ટ ડાયાગ્રામ જેવા ગાણિતક મોડેલને પણ સમાંતર સિસ્ટમની વર્તણૂક રજૂ કરવા માટે વિકસાવાયેલ છે.

ફ્લાઇનનું વર્ગીકરણ વિજ્ઞાન

[ફેરફાર કરો]માઇકલ જે. ફ્લાઇને સમાંતર (અને ક્રમિક) કમ્પ્યુટર્સ અને પ્રોગ્રામ્સ માટે સૌથી પ્રથમ વર્ગીકરણ પદ્ધતિ પૈકી એક વિકસાવી હતી જે હવે ફ્લાઇનની ટેક્સોનોમી તરીકે ઓળખાય છે. ફ્લાઇને પ્રોગ્રામ્સ અને કમ્પ્યુટર્સને તેઓ સૂચનાના સિંગલ સેટ કે અનેકવિધ સેટથી સંચાલિત થાય છે અને તે સૂચનામાં ડેટાના એક સેટનો ઉપયોગ કરતા હતા કે અનેકવિધ સેટનો ઉપયોગ થતો હતો તેના આધારે વર્ગીકૃત કર્યા હતા.

સિંગલ ઇન્સ્ટ્રક્શન સિંગલ ડેટા (એસઆઇએસડી (SISD)) વર્ગીકરણ એક સંપૂર્ણ ક્રમિક પ્રોગ્રામની સમકક્ષ છે. સિંગલ ઇન્સ્ટ્રક્શન મલ્ટિપલ ડેટા (એસઆઇએમડી (SIMD) વર્ગીકરણ સમાન કાર્યવાહી મોટા ડેટા સેટ પર વારંવાર કરવાની સમકક્ષ છે. તે સામાન્ય રીતે સિગ્નલ પ્રોસેસિંગ એપ્લિકેશન્સમાં થાય છે. મલ્ટિપલ ઇન્સ્ટ્રક્શન સિંગલ ડેટા (એમઆઇએસડી (MISD))નો ઉપયોગ વર્ગીકરણ માટે ભાગ્યે જ કરવામાં આવે છે. તેનો ઉકેલ લાવવા માટે કમ્પ્યુટર આર્કિટેક્ચરનો વિકાસ કરવામાં આવ્યો હતો, (જેમ કે સિસ્ટોલિક સંગ્રહ), પરંતુ આ વર્ગમાં બંધ બેસી શકે તેવા બહુ ઓછા એપ્લિકેશન્સ તૈયાર થયા હતા. મલ્ટિપલ ઇન્સ્ટ્રક્શન મલ્ટિપલ ડેટા (એમઆઇએમડી (MIMD)) પ્રોગ્રામ સમાંતર પ્રોગ્રામ્સનો સૌથી સામાન્ય પ્રકાર છે.

ડેવિડ એ. પેટર્સન અને જોન એલ. હેનેસીના જણાવ્યા પ્રમાણે, “અલબત્ત, કેટલાક મશીન આ કેટેગરીના મિશ્રણ હોય છે, પરંતુ આ મોડલ ટકી રહ્યું છે કારણ કે તે સરળ છે, સમજવામાં સહેલું છે અને બહુ સારો પ્રાથમિક અંદાજ આપે છે. તે કદાચ તેની સમજણપાત્રતાના કારણે સૌથી વધુ ઉપયોગમાં લેવાતી સ્કીમ છે.”[૧૭]

સમાંતરણના પ્રકાર

[ફેરફાર કરો]બિટ-લેવલ સમાંતરણ

[ફેરફાર કરો]1970ના દાયકાથી વેરી લાર્જ સ્કેલ ઇન્ટીગ્રેશન (વીએલએસઆઇ (VLSI)) કમ્પ્યુટર ચિપ ફેબ્રિકેશન ટેકનોલોજીના આગમનથી લગભગ 1986 સુધી કમ્પ્યુટર આર્કિટેક્ચરમાં ઝડપ વધારવા માટે તેની કમ્પ્યુટર વર્ડ સાઇઝ- પ્રોસેસર દરેક ચક્રમાં જે માહિતી પર કામ કરી શકે છે તેનું પ્રમાણ –બમણું કરવામાં આવતું હતું.[૧૮] વર્ડ સાઇઝ વધારવાથી પ્રોસેસરે શબ્દની લંબાઇથી વધુ મોટું કદ ધરાવતા વેરિયેબલ્સ પર કામગીરી લાગુ કરવા જે સૂચનાઓનું પાલન કરવું પડે છે તેમાં ઘટાડો થાય છે. ઉદાહરણ તરીકે 8 બિટ પ્રોસેસરે બે 16 બિટના ઇન્ટીગર્સ ઉમેરવા પડે છે ત્યારે પ્રોસેસરે સૌથી પહેલા દરેક ઇન્ટીગરમાંથી સ્ટાન્ડર્ડ ઉમેરાની સૂચનાનું પાલન કરીને 8 નીચા ક્રમના બિટ્સ ઉમેરવા પડે છે, ત્યાર બાદ 8 ઊંચા ક્રમના બિટ્સને એડ-વિથ-કેરી સૂચના સાથે અને કેરી બિટને નીચેના ક્રમના ઉમેરા સાથે ઉમેરવા પડે છે. આ રીતે 8-બિટ પ્રોસેસર માટે એક કામગીરી પૂર્ણ કરવા માટે બે સૂચનાઓની જરૂર પડે છે જેમાં 16 બિટ પ્રોસેસર સિંગલ સૂચના સાથે કામગીરી પૂરી કરવા માટે સક્ષમ હશે.

ઐતિહાસિક રીતે 4- બિટ માઇક્રોપ્રોસેસર્સની જગ્યાએ 8- બિટના, ત્યાર બાદ 16-બિટના અને ત્યાર પછી 32-બિટના માઇક્રોપ્રોસેસર્સ આવ્યા હતા. 32 બિટના પ્રોસેસર્સના આગમન સાથે આ ટ્રેન્ડનો સામાન્ય રીતે અંત આવ્યો હતો, જે બે દાયકાથી સામાન્ય હેતુના કમ્પ્યુટિંગમાં ધોરણ હતું. તાજેતરમાં (2003-2004)માં x86-64 આર્કિટેક્ચરના આગમન બાદ 64- બિટ પ્રોસેસર્સ સામાન્ય બન્યા છે.

સૂચના-સ્તર સમાંતરણ

[ફેરફાર કરો]

કમ્પ્યુટર પ્રોગ્રામ હકીકતમાં સૂચનાઓની એક શૃંખલા છે જે પ્રોસેસર દ્વારા લાગુ થાય છે. આ સૂચનાઓને પુનઃક્રમાંકિત કરી શકાય છે અને જૂથમાં જોડી શકાય છે જેને ત્યાર બાદ પ્રોગ્રામના પરિણામમાં ફેરફાર કર્યા વગર સમાંતર રીતે લાગુ કરી શકાય છે. તેને સૂચના-સ્તરના સમાંતરણ તરીકે ઓળખવામાં આવે છે. સૂચના-સ્તર સમાંતરણની પ્રગતિએ 1980ના દાયકાથી 1990ના દાયકાના મધ્ય સુધી કમ્પ્યુટર આર્કિટેક્ચર પર પોતાનો પ્રભુત્વ જમાવ્યું હતું.[૧૯]

આધુનિક પ્રોસેસર્સમાં બહુ-તબક્કાની સૂચના પાઇપલાઇન્સ હોય છે. પાઇપલાઇનમાં દરેક તબક્કો જે તે તબક્કાની સૂચના પર પ્રોસેસરની વિવિધ કામગીરી સાથે સંબંધિત હોય છે, એન (N) - તબક્કાની પાઇપલાઇન ધરાવતો પ્રોસેસર એન (N) વિવિધ સૂચનાઓ હોય છે જે પૂર્ણ થવાના વિવિધ તબક્કામાં હોય છે. પાઇપલાઇન પ્રોસેસરનો કેનોનિકલ ઉદાહરણ આરઆઇએસસી (RISC) પ્રોસેસર છે જેમાં પાંચ તબક્કા, સૂચના ફેચ, ડિકોડ, એક્ઝિક્યુટ, મેમરી એક્સેસ અને રાઇટ બેક હોય છે. પેન્ટિયમ 4 પ્રોસેસરમાં 35-તબક્કાની પાઇપલાઇન હતી.[૨૦]

પાઇપલાઇનિંગમાં સૂચના-સ્તરના સમાંતરણના ઉમેરા ઉપરાંત અમુક પ્રોસેસર્સ એક સમયે એકથી વધુ સૂચના આપી શકે છે. તેને સુપરસ્કેલર પ્રોસેસર્સ તરીકે ઓળખવામાં આવે છે. સૂચનાઓ વચ્ચે ડેટા ડિપેન્ડન્સી ન હોય તો તેને એક જૂથમાં ગોઠવી શકાય છે. સ્કોરબોર્ડિંગ અને ટોમાસુલો એલ્ગોરિધમ (જે સ્કોરબોર્ડિંગ જેવું જ છે, પરંતુ રજિસ્ટર પુનઃનામકરણનો ઉપયોગ કરે છે) એ ક્રમ સિવાયના અમલીકરણ અને સૂચના સ્તરના સમાંતરણની બે સૌથી સામાન્ય તકનીક છે.

ડેટા સમાંતરણ

[ફેરફાર કરો]ડેટા સમાંતરણ પ્રોગ્રામ લૂપ્સમાં વારસામાં મળતું સમાંતરણ છે જે ડેટાને વિવિધ કમ્પ્યુટિંગ નોડ્સ પર સમાંતર પ્રોસેસ થવા માટે વિતરિત કરે છે. “સમાંતરણ લૂપ્સમાં ઘણી વાર સમાન (એક સરખા હોય તે જરૂરી નથી) કામગીરીનો ક્રમ રચાય છે અથવા મોટા ડેટા માળખાના તત્વો પર કામગીરી થાય છે.”[૨૧] ઘણા વૈજ્ઞાનિક અને એન્જિનિયરિંગ એપ્લિકેશન્સ ડેટા સમાંતરણ રજૂ કરે છે.

લૂપ વાહક ડિપેન્ડન્સી એ એક કે વધારે પૂર્વ ઇટરેશન પર લૂપ ઇટરેશનનો આધાર છે. લૂપ વાહક ડિપેન્ડન્સી લૂપ્સના સમાંતરણને અટકાવે છે. ઉદાહરણ તરીકે નીચેના સ્યુડોકોડનો વિચાર કરો જે પ્રથમ કેટલાક ફિબોનાકી નંબર્સની ગણતરી કરે છે.

1: PREV1 := 0 2: PREV2 := 1 4: do: 5: CUR := PREV1 + PREV2 6: PREV1 := PREV2 7: PREV2 := CUR 8: જ્યારે (CUR < 10)

આ લૂપને સમાંતર કરી શકાતી નથી કારણ કે સીયુઆર (CUR) પોતાના પર (PREV2) અને PREV1 પર આધારિત છે. જે દરેક લૂપ ઇટરેશન પર ગણવામાં આવે છે. દરેક ઇટરેશન અગાઉના પરિણામ પર આધારિત હોય છે તેથી તેને સમાંતર કરી શકાતું નથી. કૂટપ્રશ્નનું કદ મોટું થાય છે તેમ ઉપલબ્ધ ડેટા સમાંતરનું પ્રમાણ પણ વધતું જાય છે.[૨૨]

ટાસ્ક સમાંતરણ

[ફેરફાર કરો]ટાસ્ક સમાંતરણ એ સમાંતર પ્રોગ્રામની એક લાક્ષણિકતા છે જે મુજબ “એકદમ અલગ ગણતરીઓ ડેટાના સમાન અથવા અલગ સેટ પર થઈ શકે છે.”[૨૧] તે ડેટા સમાંતરણથી વિપરીત છે જ્યાં સમાન ગણતરી ડેટાના સમાન અથવા અલગ સેટ પર કરવામાં આવે છે. ટાસ્ક સમાંતરણ સામાન્ય રીતે કૂટપ્રશ્નના કદની સાથે વધતું નથી.[૨૨]

હાર્ડવેર

[ફેરફાર કરો]મેમરી અને કમ્યુનિકેશન

[ફેરફાર કરો]સમાંતર કમ્પ્યુટરમાં મુખ્ય મેમરી શેર્ડ મેમરી (સિંગલ એડ્રેસ સ્પેસમાં તમામ પ્રોસેસિંગ ઘટકો સાથે હિસ્સેદારી) અથવા ડિસ્ટ્રિબ્યુટેડ મેમરી (જેમાં દરેક પ્રોસેસિંગ ઘટકનો પોતાનો સ્થાનિક એડ્રેસ સ્પેસ હોય છે) હોય છે.[૨૩] ડિસ્ટ્રિબ્યુટેડ મેમરી એ હકીકત દર્શાવે છે કે મેમરી તાર્કિક રીતે વિતરીત થઇ છે, પરંતુ ઘણી વાર દર્શાવે છે કે તેને ભૌતિક રીતે પણ વિતરીત કરવામાં આવી છે. ડિસ્ટ્રિબ્યુટેડ શેર્ડ મેમરી અને મેમરી વર્ચ્યુલાઇઝેશન બે વલણને સંયુક્ત સ્વરૂપ આપે છે જેમાં પ્રોસેસિંગ ઘટકની પોતાની સ્થાનિક મેમરી અને નોન-લોકલ પ્રોસેસર્સ પર મેમરીનું એક્સેસ હોય છે. સ્થાનિક મેમરીને એક્સેસ સામાન્ય રીતે બિન સ્થાનિક મેમરીના એક્સેસ કરતા વધુ ઝડપી હોય છે.

મુખ્ય મેમરીના દરેક તત્વને જેમાં સમાન લેટન્સી અને બેન્ડવિડ્થ સાથે એક્સેસ કરી શકાય તે કમ્પ્યુટર આર્કિટેક્ચરને યુનિફોર્મ મેમરી એક્સેસ (યુએમએ (UMA)) સિસ્ટમ્સ તરીકે ઓળખવામાં આવે છે. સામાન્ય રીતે તે શેર્ડ મેમરી સિસ્ટમથી જ પ્રાપ્ત કરી શકાય છે જેમાં મેમરી ભૌતિક રીતે ડિસ્ટ્રિબ્યુટેડ હોતી નથી. આવી પ્રોપર્ટી ન હોય તેવી સિસ્ટમ નોન-યુનિફોર્મ મેમરી એક્સેસ (એનયુએમએ (NUMA)) આર્કિટેક્ચર તરીકે ઓળખાય છે. ડિસ્ટ્રિબ્યુટેડ મેમરી સિસ્ટમમાં નોન-યુનિફોર્મ મેમરી એક્સેસ હોય છે.

કમ્પ્યુટર સિસ્ટમ્સ કેચ - પ્રોસેસરની નજીક આવેલી નાની ઝડપી મેમરીનો ઉપયોગ કરે છે જે મેમરી મૂલ્યની કામચલાઉ નકલનો સંગ્રહ કરે છે. (ભૌતિક અને તાર્કિક દૃષ્ટિએ નજીકમાં) સમાંતર કમ્પ્યુટર સિસ્ટમ્સને કેચિસ સાથે કૂટપ્રશ્ન થઈ શકે છે જે એક કરતા વધુ સ્થળે સમાન મૂલ્યનો સંગ્રહ કરતી હોય, જેમાં ખોટા પ્રોગ્રામ અમલીકરણની શક્યતા રહે છે. આ કમ્પ્યુટર્સને કેચ કોહરન્સી સિસ્ટમની જરૂર પડે છે જે કેચના મૂલ્ય પર નજર રાખે છે અને વ્યૂહાત્મક રીતે તેને શૂદ્ધ કરે છે, જેનાથી યોગ્ય પ્રોગ્રામનો અમલ થાય તેની ખાતરી થાય છે. કયા મૂલ્યને એક્સેસ કરવામાં આવી રહ્યા છે (અને તેથી શુદ્ધ કરવાની જરૂર છે) તેના પર નજર રાખવાની સૌથી સામાન્ય પદ્ધતિ બસ સ્નૂપિંગ છે. વિશાળ, ઉચ્ચ પ્રદર્શન કેચ સાતત્યસભર માળખા ડિસ્ટ્રિબ્યુટેડ મેમરી સિસ્ટમ્સની જેમ સંતુલન સાધતું નથી. પરિણામે, શેર્ડ મેમરી કમ્પ્યુટર આર્કિટેક્ટર ડિસ્ટ્રિબ્યુટેડ મેમરી સિસ્ટમ જેટલા સ્કેલ કરી શકતા નથી.[૨૩]

પ્રોસેસર- પ્રોસેસર અને પ્રોસેસર-મેમરી કોમ્યુનિકેશન વિવિધ રીતે હાર્ડવેરમાં હિસ્સા આધારિત (મલ્ટિપોર્ટેડ અથવા મલ્ટિપ્લેક્સ્ડ) મેમરી, એક ક્રોસબાર સ્વિચ, એક હિસ્સેદારી આધારિત બસ અથવા આંતરિક રીતે સંકળાયેલા સ્ટાર, રિંગ, ટ્રી, હાઇપરક્યુબ, ફેટ હાઇબરક્યુબ (નોડ પર એકથી વધુ પ્રોસેસર ધરાવતું હાઇબરક્યુબ) ટોપોલોજી મારફત અથવા એન-પરિમાણિય જાળથી પણ વિવિધ રીતે લાગુ કરી શકાય છે.

આંતરિક રીતે સંકળાયેલા નેટવર્ક્સ પર આધારિત સમાંતર કમ્પ્યુટર્સમાં એક બીજા સાથે જોડાયેલા ન હોય તેવા નોડ વચ્ચે સંદેશ પસાર કરવા માટે અમુક પ્રકારના રાઉટિંગની જરૂર પડે છે. પ્રોસેસર્સ વચ્ચે કોમ્યુનિકેશન માટે ઉપયોગમાં લેવાતું માધ્યમ વિશાળ મલ્ટિપ્રોસેસર મશીનમાં ચોક્કસ ક્રમમાં હોઇ શકે છે.

સમાંતર કમ્પ્યુટર્સના વર્ગ

[ફેરફાર કરો]સમાંતર કમ્પ્યુટર્સને તેના હાર્ડવેર કેટલા અંશે સમાંતરણને ટેકો આપે છે તેના આધારે ઉપરછલ્લી રીતે વર્ગીકૃત કરી શકાય છે. આ વર્ગીકરણ પાયાના કમ્પ્યુટિંગ નોડ્સ વચ્ચેના અંતરના સમપ્રમાણમાં હોય છે. તે પરસ્પર એક્સક્લુઝિવ નથી, ઉદાહરણ તરીકે સિમેટ્રીક મલ્ટિપ્રોસેસર્સના ઝુમખા પ્રમાણમાં સામાન્ય છે.

મલ્ટિકોર કમ્પ્યુટિંગ

[ફેરફાર કરો]મલ્ટિકોર પ્રોસેસર એ એવું પ્રોસેસર છે જેમાં એક જ ચિપ પર એકથી વધુ અમલીકરણ એકમો (“કોર”) આવેલા હોય છે. સુપરસ્કેલર પ્રોસેસર્સ કરતા આ પ્રોસેસર અલગ હોય છે. સુપરસ્કેલર પ્રોસેસર્સ એક સૂચનાના પ્રવાહ (થ્રેડ)માંથી પ્રતિ ચક્ર એકથી વધુ સૂચનાઓ આપી શકે છે, તેની સરખામણીમાં મલ્ટિકોર પ્રોસેસર એકથી વધુ સૂચના પ્રવાહ મારફત પ્રતિ ચક્ર એકથી વધુ સૂચનાઓ આપી શકે છે. મલ્ટિકોર પ્રોસેસરમાં દરેક કોર સુપરસ્કેલર બનવાની સંભાવના ધરાવતા હોય છે, જેમાં દરેક ચક્રમાં દરેક કોર એક સૂચના પ્રવાહમાંથી એકથી વધુ સૂચનાઓ ઇશ્યૂ કરી શકે છે.

સાઇમલ્ટેનિયસ (એક સાથે) મલ્ટિથ્રિડિંગ (ઇન્ટેલનું હાઇપરથ્રેડિંગ જેનું સૌથી જાણીતું ઉદાહરણ છે) સ્યુડો-મલ્ટિકોરિઝમનું પ્રારંભિક ઉદાહરણ હતું. એક સાથે મલ્ટિથ્રેડિંગ માટે સક્ષમ પ્રોસેસરમાં માત્ર એક અણલીકરણ એકમ (“કોર”) હોય છે, પરંતુ જ્યારે અમલીકરણ એકમ કામ કરતું ન હોય (જેમ કે કેચ મિસ દરમિયાન) તે બીજી થ્રેડને પ્રોસેસ કરવા માટે અમલીકરણ એકમનો ઉપયોગ કરે છે. સોની પ્લેસ્ટેશન 3માં ઉપયોગ માટે તૈયાર કરવામાં આવેલું આઇબીએમ (IBM)નું સેલ માઇક્રોપ્રોસેસર અન્ય અગ્રણી મલ્ટિકોર પ્રોસેસર છે.

સિમેટ્રિક મલ્ટિપ્રોસેસિંગ

[ફેરફાર કરો]સિમેટ્રિક મલ્ટિપ્રોસેસર (એસએમપી (SMP)) એકથી વધુ એક સરખા પ્રોસેસર્સ ધરાવતી એક કમ્પ્યુટર સિસ્ટમ છે જે મેમરીમાં હિસ્સેદારી કરે છે અને બસ દ્વારા જોડાય છે.[૨૪] બસ કન્ટેન્શનથી બસના આર્કિટેક્ચરનું સ્કેલિંગ અટકે છે. પરિણામે એસએમપી (SMP)માં સામાન્ય રીતે 32થી વધુ પ્રોસેસર્સ હોતા નથી.[૨૫] “પૂરતા પ્રમાણમાં મેમરી બેન્ડવિડ્થ હોય તો પ્રોસેસર્સના નાના કદ અને મોટા કેચ દ્વારા બસ બેન્ડવિડ્થની જરૂરિયાતમાં નોંધપાત્ર ઘટાડાના કારણે આવી સિમેટ્રિક મલ્ટિપ્રોસેસર્સ ખર્ચની બાબતમાં અત્યંત અસરકારક હોય છે.”[૨૪]

ડિસ્ટ્રિબ્યુટેડ કમ્પ્યુટિંગ

[ફેરફાર કરો]ડિસ્ટ્રિબ્યુટેડ કમ્પ્યુટર (જે ડિસ્ટ્રિબ્યુટેડ મેમરી મલ્ટિપ્રોસેસર તરીકે પણ ઓળખાય છે) એક ડિસ્ટ્રિબ્યુટેડ મેમરી કમ્પ્યુટર સિસ્ટમ છે જેમાં પ્રોસેસિંગ ઘટકોને એક નેટવર્ક દ્વારા સાંકળવામાં આવે છે. ડિસ્ટ્રિબ્યુટેડ કમ્પ્યુટર્સ ઉચ્ચ પ્રમાણમાં ક્ષમતા વધારી શકાય તેવા હોય છે.

ક્લસ્ટર કમ્પ્યુટિંગ

[ફેરફાર કરો]

ક્લસ્ટર એ એક બીજા સાથે જોડાયેલા કમ્પ્યુટર્સ હોય છે જે સાથે કામ કરે છે જેથી અમુક રીતે તેમને સિંગલ કમ્પ્યુટર તરીકે ગણી શકાય.[૨૬] ક્લસ્ટર્સ એકથી વધુ સ્વતંત્ર મશીન્સના બનેલા હોય છે જે નેટવર્કથી જોડાયેલા હોય છે. ક્લસ્ટર્સના મશીનમાં સિમેટ્રિક હોતા નથી ત્યારે લોડ બેલેન્સિંગ વધારે મુશ્કેલ બને છે. ક્લસ્ટરનો સૌથી સામાન્ય પ્રકાર બ્યુવુલ્ફ ક્લસ્ટરર છે જે એકથી વધુ એક સમાન કમર્શિયલ ઓફ-ધી-શેલ્ફ કમ્પ્યુટર્સ પર લાગુ પાડવામાં આવે છે જે ટીસીપી/ટીપી (TCP/IP) ઇથરનેટ લોકલ એરિયા નેટવર્ક સાથે સંકળાયેલ છે.[૨૭] બ્યુવુલ્ફ ટેકનોલોજી થોમસ સ્ટર્લિંગ અને ડોનાલ્ડ બેકર દ્વારા અસલમાં વિકસાવવામાં આવ્યું હતું. ટોપ500 (TOP500)સુપર કમ્પ્યુટર્સના મોટા ભગના ક્લસ્ટર્સ છે.[૨૮]

મેસિવ (જંગી) પેરલલ પ્રોસેસિંગ

[ફેરફાર કરો]મેસિવલી પેરલલ પ્રોસેસર (એમપીપી (MPP)) અનેક નેટવર્કડ પ્રોસેસર્સ સાથેનું સિંગલ કમ્પ્યુટર છે. એમપીપી (MPP)માં ક્લસ્ટર્સ જેવી ઘણી વિશેષતાઓ હોય છે, પરંતુ એમપીપી (MPP) માં વિશિષ્ટ ઇન્ટરકનેક્ટ નેટવર્ક્સ હોય છે (જ્યાં નેટવર્કિંગ માટે ક્લસ્ટર્સ કોમોડિટી હાર્ડવેરનો ઉપયોગ કરે છે). એમપીપી (MPP) ક્લસ્ટર્સ કરતા મોટા હોય છે જેમાં સામાન્ય રીતે 100થી ઘણા વધારે પ્રોસેસર્સ હોય છે.[૨૯] એમપીપી (MPP)માં “દરેક સીપીયુ (CPU)માં પોતાની મેમરી અને ઓપરેટિંગ સિસ્ટમ અને એપ્લિકેશનની નકલ હોય છે. દરેક સબસિસ્ટમ બીજા સાથે હાઇ સ્પીડ ઇન્ટરકનેક્ટ મારફત પ્રત્યાયન કરે છે.”[૩૦]

જૂન 2009ના TOP500 રેન્કિંગ પ્રમાણે વિશ્વનું પાંચમા ક્રમનું સૌથી ઝડપી સુપરકમ્પ્યુટર બ્લુ જીન/એલ (Blue Gene/L) એક એમપીપી (MPP) છે.

ગ્રીડ કમ્પ્યુટિંગ

[ફેરફાર કરો]ગ્રીડ કમ્પ્યુટિંગ સમાંતર કમ્પ્યુટિંગનું સૌથી વધુ ડિસ્ટ્રિબ્યુટેડ પ્રકાર છે. તેમાં આપેલી કૂટપ્રશ્ન પર કામ કરવા માટે ઇન્ટરનેટ પર પ્રત્યાયન કરતા કમ્પ્યુટર્સનો ઉપયોગ કરે છે. ઇન્ટરનેટ પર ઉપલબ્ધ નીચા બેન્ડવિડ્થ અને અત્યંત ઊંચા લેટેન્સીના કારણે ગ્રીડ કમ્પ્યુટિંગ માત્ર એમ્બ્રેસિંગ પેરલલ કૂટપ્રશ્નઓ પર જ કામ કરે છે. ઘણા ગ્રીડ કમ્પ્યુટિંગ એપ્લિકેશન્સ રચવામાં આવ્યા છે જેમાંથી SETI@home અને Folding@Home સૌથી જાણીતા ઉદાહરણ છે.[૩૧]

મોટા ભાગના ગ્રીડ કમ્પ્યુટિંગ એપ્લિકેશન્સમાં મિડલવેરનો ઉપયોગ થાય છે જે એક સોફ્ટવેર છે અને નેટવર્ક સ્રોતોના સંચાલન અને સોફ્ટવેરને સ્ટાન્ડર્ડાઇઝ કરવા ઓપરેટિંગ સિસ્ટમ અને એપ્લિકેશન વચ્ચે રહે છે. સૌથી સામાન્ય ગ્રીડ કમ્પ્યુટિંગ મિડલવેર બ્લેકબેરી ઓપન ઇન્ફ્રાસ્ટ્રક્ચર ફોર નેટવર્ક કમ્પ્યુટિંગ (બીઓઆઇએનસી (BOINC)) છે. ઘણી વાર, ગ્રીડ કમ્પ્યુટિંગ સોફ્ટવેર “સ્પેર સાઇકલ”નો ઉપયોગ કરે છે, કમ્પ્યુટર કામ ન કરતું હોય ત્યારે ગણતરીઓ કરે છે.

સ્પેશિયલાઇઝ્ડ સમાંતર કમ્પ્યુટર્સ

[ફેરફાર કરો]સમાંતર કમ્પ્યુટિંગમાં સ્પેશિયલાઇઝ્ડ સમાંતર ડિવાઇસ (ઉપકરણ) હોય છે જે ઉચ્ચ પ્રકારના રસનો વિષય છે. તે ડોમેઇનલક્ષી ન હોવા છતાં સમાંતર કૂટપ્રશ્નના અમુક વર્ગમાં જ લાગુ થઇ શકે છે.

ફિલ્ડ પ્રોગ્રામેબલ ગેટ સંગ્રહ સાથે રિકન્ફિગરેબલ કમ્પ્યુટિંગ

[ફેરફાર કરો]રિકન્ફિગરેબલ કમ્પ્યુટિંગ એ સામાન્ય હેતુના કમ્પ્યુટર માટે સહ-પ્રોસેસર તરીકે ફિલ્ડ પ્રોગ્રામેબલ ગેટ એરેઝ (એફપીજીએ (FPGA))નો ઉપયોગ છે. એફપીજીએ (FPGA) એ કમ્પ્યુટર ચિપ છે જે તેને સોંપવામાં આવેલા ટાસ્કને રિરાઇટ કરી શકે છે.

એફપીજીએ (FPGA)ને વીએચડીએલ (VHDL) અથવા વેરિલોગ જેવી હાર્ડવેર વર્ણન ભાષાઓ (લેંગ્વેજ) દ્વારા પ્રોગ્રામ કરી શકાય છે. પરંતુ આ લેંગ્વેજમાં પ્રોગ્રામિંગ થકવી નાખનારું હોઇ શકે છે. કેટલાક વેન્ડર્સે સી (C) ટુ એચડીએલ (HDL) લેંગ્વેજ માટે સી (C) વિકસાવ્યું છે જે સી પ્રોગ્રામિંગ લેંગ્વેજના સિન્ટેક્સ અને/અથવા સિમેન્ટિક્સને અનુસરવાનો પ્રયાસ કરે છે. સી (C) ટુ એચડીએલ (HDL) લેંગ્વેજમાં મિટ્રિયોન-સી, ઇમ્પલ્સ સી, ડીઆઇએમઇ-સી (DIME-C) અને હેન્ડેલ-સીનો સમાવેશ થાય છે. C++ પર આધારિત સિસ્ટેમ સીના ચોક્કસ સબસેટ પણ આ હેતુ માટે ઉપયોગમાં લઇ શકાય છે.

એએમડી (AMD)એ તેની હાઇપરટ્રાન્સપોર્ટ ટેકનોલોજી થર્ડ પાર્ટી વેન્ડર્સ માટે ખુલ્લી મૂકવાનો નિર્ણય લીધો તે ઉચ્ચ સ્તરીય કન્ફિગરેબલ કમ્પ્યુટિંગ માટે સક્ષમ ટેકનોલોજી બની છે.[૩૨] ડીઆરસી કમ્પ્યુટર કોર્પોરેશનના ચીફ ઓપરેટિંગ ઓફિસર માઇકલ આર. ડીમોરના જણાવ્યા પ્રમાણે “અમે જ્યારે પ્રથમ વાર એએમડી (AMD)માં ગયા ત્યારે તેમણે અમને “સોકેટ ચોર” ગણાવ્યા હતા. હવે તેઓ અમને પાર્ટનર ગણે છે.”[૩૨]

જનરલ પર્પઝ કમ્પ્યુટિંગ ઓન ગ્રાફિક્સ પ્રોસેસિંગ યુનિટ્સ (જીપીજીપીયુ (GPGPU))

[ફેરફાર કરો]

જનરલ પર્પઝ કમ્પ્યુટિંગ ઓન ગ્રાફિક્સ પ્રોસેસિંગ યુનિટ્સ (જીપીજીપીયુ (GPGPU)) કમ્પ્યુટર એન્જિનિયરિંગ રિસર્ચમાં તાજેતરનો ટ્રેન્ડ છે. જીપીયુ (GPU) કો-પ્રોસેસર્સ છે જે કમ્પ્યુટર ગ્રાફિક્સ પ્રોસેસિંગ માટે મહત્તમ ઉપયોગમાં લેવાઇ રહ્યા છે.[૩૩] કમ્પ્યુટર ગ્રાફિક્સ ખાસ કરીને લિનીયર એલ્જિબ્રા મેટ્રિક્સ કામગીરીમાં પ્રોસેસિંગ ડેટા સમાંતર પ્રક્રિયાનું પ્રભુત્વ ધરાવતું ફિલ્ડ છે.

પ્રારંભિક દિવસોમાં જીપીજીપીયુ (GPGPU) પ્રોગ્રામ્સમાં સામાન્ય ગ્રાફિક્સ એપીઆઇ (API)નો ઉપયોગ પ્રોગ્રામ્સના અમલીકરણ માટે થાય છે. જોકે, તાજેતરમાં કેટલાક નવા પ્રોગ્રામ લેંગ્વેજ અને પ્લેટફોર્મ્સનો ઉપયોગ જીપીયુ (GPU) પર સામાન્ય હેતુના કમ્પ્યુટેશન માટે થાય છે જેમાં એનવિડિયા (Nvidia) અને એએમડીએ (AMD) અનુક્રમે સીયુડીએ (CUDA) અને સીટીએમ (CTM) માટે પ્રોગ્રામિંગ એન્વાયર્નમેન્ટ રજૂ કર્યા છે. અન્ય જીપીયુ (GPU) પ્રોગ્રામિંગ લેંગ્વેજમાં બ્રુકજીપીયુ, પીકસ્ટ્રીમ અને રેપિડમાઇન્ડ સામેલ છે. એનવિડિયાએ પણ ટેસ્લા શ્રેણીમાં ગણતરી માટે ચોક્કસ પ્રોડક્ટ્સ રજૂ કરી છે.

એપ્લિકેશનલક્ષી સંકલિત સર્કિટ્સ

[ફેરફાર કરો]સમાંતર એપ્લિકેશન્સ સાથે કામ કરવા માટે કેટલાક એપ્લિકેશન સ્પેસિફિક ઇન્ટીગ્રેટેડ સર્કિટ (એએસઆઇસી (ASIC)) વિકસાવવામાં આવી છે.[૩૪][૩૫][૩૬]

એએસઆઇસી (ASIC) વ્યાખ્યાથી ચોક્કસ એપ્લિકેશનલક્ષી હોવાથી તેને તે એપ્લિકેશન માટે સંપૂર્ણપણે લાગુ કરી શકાય છે. પરિણામે આપેલા એપ્લિકેશન માટે એએસઆઇસી (ASIC) સામાન્ય હેતુના કમ્પ્યુટરને પાછળ રાખી દે છે. જોકે, એએસઆઇસી (ASIC)ને એક્સ –રે લિથોગ્રાફી દ્વારા રચવામાં આવે છે. આ પ્રક્રિયામાં માસ્કની જરૂર પડે છે જે ઘણું ખર્ચાળ હોઇ શકે છે. એક સિંગલ માસ્કની કિંમત એક મિલિયન યુએસ ડોલરથી વધુ હોઇ શકે છે.[૩૭] (ચિપ માટે જેટલા નાના ટ્રાન્ઝિસ્ટરની જરૂર હોય તેટલા પ્રમાણમાં માસ્ક મોંઘું હશે.) દરમિયાન સમયની સાથે સામાન્ય હેતુના કમ્પ્યુટિંગમાં કામગીરીમાં વધારો થાય છે (મૂરેના નિયમમાં સમજુતી પ્રમાણે) જેનાથી એક કે બે ચિપ પેઢીઓમાં લાભ ધોવાઇ જાય છે.[૩૨] ઉચ્ચ પ્રારંભિક ખર્ચ મૂરના નિયમલક્ષી સામાન્ય હેતુ ગણનને પાછળ રાખી દેવાના વલણથી એએસઆઇસી (ASIC) મોટા ભાગના સમાંતર કમ્પ્યુટિંગ એપ્લિકેશન્સ માટે બિનઉપયોગી બન્યું છે. જોકે કેટલાક બાંધવામાં આવ્યા છે. તેમાંથી એક ઉદાહરણ પેટા-ફ્લોપ રિકેન એમડીગ્રેપ-3 (RIKEN MDGRAPE-3) મશીન છે જેમાં મોલેક્યુલર ડાયનેમિક્સ સિમ્યુલેશન માટે કસ્ટમ એએસઆઇસી (ASIC)નો ઉપયોગ થાય છે.

વેક્ટર પ્રોસેસર્સ

[ફેરફાર કરો]

વેક્ટર પ્રોસેસર એ સીપીયુ (CPU) અથવા કમ્પ્યુટર સિસ્ટમ છે જે મોટા પ્રમાણમાં ડેટા પર સમાન સૂચના લાગુ પાડી શકે છે. “વેક્ટર પ્રોસેસર્સમાં ઉચ્ચ સ્તરીય કામગીરી હોય છે જે વિવિધ વેક્ટર્સના લિનીયર સંગ્રહ પર કામ કરે છે. વેક્ટર કામગીરીનું એક ઉદાહરણ A = B × C છે જ્યાં A , B , અને C દરેક 64 બિટ ફ્લોટિંગ પોઇન્ટ સંખ્યાના 64 એલિમેન્ટ વેક્ટર છે."[૩૮] તેઓ ફ્લાઇનના એસઆઇએમડી (SIMD) વર્ગીકરણ સાથે નિકટતાથી સંકળાયેલા છે.[૩૮]

ક્રે કમ્પ્યુટર્સ 1970ના અને 1980ના દાયકામાં તેમના વેક્ટર-પ્રોસેસિંગ કમ્પ્યુટર્સના કારણે લોકપ્રિય બન્યા હતા. જોકે વેક્ટર પ્રોસેસર્સ – સીપીયુ (CPU) તથા ફુલ કમ્પ્યુટર સિસ્ટમ્સ – સામાન્ય રીતે અદૃશ્ય થયા છે. આધુનિક પ્રોસેસર ઇન્સ્ટ્રક્શન સેટ એલ્ટીવેક અને સ્ટ્રીમિંગ એસઆઇએમડી (SIMD) એક્સ્ટેન્શન્સ (એસએસઇ (SSE)) જેવા કેટલાક સામાન્ય વેક્ટર પ્રોસેસિંગ સૂચનાઓ ધરાવે છે.

સોફ્ટવેર

[ફેરફાર કરો]સમાંતર પ્રોગ્રામિંગ લેંગ્વેજિસ

[ફેરફાર કરો]કોન્કરન્ટ પ્રોગ્રામિંગ લેંગ્વેજિસ, લાઇબ્રેરીઓ, એપીઆઇ (APIs) અને સમાંતર પ્રોગ્રામિંગ મોડલ્સ (જેમ કે એલ્ગોરિધમિક સ્કેલેટન્સ)ની રચના સમાંતર કમ્પ્યુટર્સના પ્રોગ્રામિંગ માટે કરવામાં આવી છે. તેને સામાન્ય રીતે તેઓ મેમરી આર્કિટેક્ચર (માળખા) વિશે જે ધારણા રચે તેના આધારે વર્ગોમાં વિભાજિત કરવામાં આવે છે જેમાં શેર્ડ મેમરી, ડિસ્ટ્રિબ્યુટેડ મેમરી અથવા શેર્ડ ડિસ્ટ્રિબ્યુટેડ મેમરીનો સમાવેશ થાય છે. શેર્ડ મેમરી પ્રોગ્રામિંગ લેંગ્વેજિસ શેર્ડ મેમરીના વેરિયેબલ્સમાં ફેરફાર કરીને પ્રત્યાયન કરે છે. ડિસ્ટ્રિબ્યુટેડ મેમરીમાં મેસેજ પસાર કરવાનો ઉપયોગ થાય છે. પીઓએસઆઇએક્સ (POSIX) થ્રેડ્સ અને ઓપનએમપી (OpenMP) બે સૌથી વધુ ઉપયોગમાં લેવાતા શેર્ડ મેમરી એપીઆઇ (APIs) છે, જ્યાં મેસેજ પાસિંગ ઇન્ટરફેસ (એમપીઆઇ) (MPI) સૌથી વધુ ઉપયોગમાં લેવાતી મેસેજ પાસિંગ સિસ્ટમ એપીઆઇ (APIs) છે.[૩૯] સમાંતર પ્રોગ્રામ્સના પ્રોગ્રામિંગમાં ઉપયોગમાં લેવાતો એક કન્સેપ્ટ ફ્યુચર કન્સેપ્ટ (ભવિષ્યનો કન્સેપ્ટ) છે જેમાં પ્રોગ્રામનો એક ભાગ ભવિષ્યમાં કોઇ સમયે પ્રોગ્રામના અન્ય ભાગ દ્વારા જરૂરી ડેટમ પૂરો પાડવાની ખાતરી આપે છે.

ઓટોમેટિક સમાંતરણ

[ફેરફાર કરો]કમ્પાઇલર દ્વારા ક્રમિક પ્રોગ્રામનું ઓટોમેટિક સમાંતરણ એ સમાંતર કમ્પ્યટિંગની હોલી ગ્રેઇલ છે. કમ્પાઇલર રિસર્ચના દાયકાઓના કામ છતાં ઓટોમેટિક સમાંતરણને માત્ર મર્યાદિત સફળતા જ મળી શકી છે.[૪૦]

મેઇનસ્ટ્રીમ (મુખ્ય) સમાંતર પ્રોગ્રામિંગ લેંગ્વેજિસ એક્સપ્લિસિટી સમાંતર અથવા (વધુમાં વધુ) પાર્શિયલ ઇમ્પ્લિસિટ રહી શકે છે જેમાં પ્રોગ્રામર કમ્પાઇલરને સમાંતરણ માટે સૂચનાઓ આપે છે. કેટલાક પૂર્ણ નિયંત્રિત સમાંતર પ્રોગ્રામિંગ લેંગ્વેજ અસ્તિત્વ ધરાવે છે જેમ કે – સિસાલ (SISAL), પેરલલ હાસ્કેલ, અને (એફપીજીએ (FPGAs) માટે) મિટ્રિયોન-સી.

એપ્લિકેશન ચેકપોઇન્ટિંગ

[ફેરફાર કરો]કમ્પ્યુટર જેટલું વધારે મોટું અને વધુ જટિલ હશે તેટલા જ પ્રમાણમાં તેમાં ગરબડ થઈ શકશે અને તેની નિષ્ફળતા વચ્ચેનો મીન ટાઇમ એટલો જ ઓછો હશે. એપ્લિકેશન ચેકપોઇન્ટિંગ એક એવી ટેકનિક છે જેમાં કમ્પ્યુટર સિસ્ટમ એપ્લિકેશનની “તસવીર” લે છે જેમાં તમામ વર્તમાન રિસોર્સ ફાળવણી અને વેરિયેબલ હિસ્સાનો રેકોર્ડ લેવાય છે જે એક જગ્યાએ બધુ ઠાલવવા સમાન છે. કમ્પ્યુટર નિષ્ફળ જાય તો આ માહિતીનો ઉપયોગ પ્રોગ્રામને પુનઃસ્થાપિત કરવા માટે થાય છે. એપ્લિકેશન ચેકપોઇન્ટિંગનો અર્થ એ થયો કે પ્રોગ્રામને શરૂઆતથી ફરી શરૂ કરવાના બદલે ચેકપોઇન્ટથી રિસ્ટાર્ટ કરવાનો રહેશે. મહિનાઓ સુધી ચાલી શકે તેવી એપ્લિકેશન માટે તે મહત્વનું છે. એપ્લિકેશન ચેકપોઇન્ટિંગનો ઉપયોગ પ્રોસેસ માઇગ્રેશન માટે થઈ શકે છે.

એલ્ગોરિધમિક (ગણતરી) પદ્ધતિઓ

[ફેરફાર કરો]સમાંતર કમ્પ્યુટર્સ વધુ મોટા અને ઝડપી બન્યા તેના કારણે એવી કૂટપ્રશ્નઓ ઉકેલવાનું શક્ય બન્યું જેમાં અગાઉ ઘણો વધારે સમય લાગતો હતો. સમાંતર કમ્પ્યુટિંગનો ઉપયોગ બાયોઇન્ફોર્મેટિક્સ (પ્રોટિન ફોલ્ડિંગ)થી લઇને અર્થશાસ્ત્ર (ગાણિતિક ફાઇનાન્સ) સુધી અનેક ક્ષેત્રમાં થાય છે. સમાંતર કમ્પ્યુટિંગ એપ્લિકેશન્સમાં જોવા મળતી કૂટપ્રશ્નઓના સામાન્ય પ્રકાર આ મુજબ છે:[૪૧]

- ડેન્સ લિનીયર એલ્જીબ્રા

- સ્પેર્સ લિનીયર એલ્જીબ્રા

- સ્પેક્ટ્રલ મેથડ્સ (જેમ કે કૂલી- ટર્કી ફાસ્ટ ફોરિયર ટ્રાન્સફોર્મ)

- એન -બોડી પ્રોબ્લેમ્સ (જેમ કે બાર્ન્સ-હટ સ્ટીમ્યુલેશન)

- સ્ટ્રક્ચર્ડ ગ્રીડ કૂટપ્રશ્નઓ (જેમ કે લેટિસ બોલ્ત્ઝમેન પદ્ધતિઓ)

- બિનમાળખાકીય ગ્રીડ કૂટપ્રશ્નઓ (ફિનિટ એલિમેન્ટ પૃથક્કરણમાં મળેલી)

- મોન્ટે કાર્લો સિમ્યુલેશન

- સંયુક્ત તર્ક (જેમ કે બ્રુટ ફોર્સ ક્રિપ્ટોગ્રાફિક ટેકનિક્સ)

- ગ્રાફ ટ્રાવેર્સલ (જેમ કે સોર્ટિંગ એલ્ગોરિધમ્સ)

- ડાયનેમિક પ્રોગ્રામિંગ

- બ્રાન્ચ અને બાઉન્ડ પદ્ધતિઓ

- ગ્રાફિકલ મોડેલ્સ (જેમ કે છુપા માર્કોવ મોડલ શોધવા અને બેરિસિયન નેટવર્કનું સર્જન)

- ફિનિટ સ્ટેટ મશીન સિમ્યુલેશન

ઇતિહાસ

[ફેરફાર કરો]

ખરા (એમઆઇએમડી) (MIMD) સમાંતરણનો ઇતિહાસ ફેડેરિકો લુઇગી, કોન્ટે મેનાબ્રિયા અને તેના “સ્કેચ ઓફ ધ એનાલિટિક એન્જિન ઇન્વેન્ટેડ બાય ચાર્લ્સ બેબેજ” સુધી જાય છે.[૪૨][૪૩] આઇબીએમ (IBM)એ એક પ્રોજેક્ટ દ્વારા 1954માં 704 લોન્ચ કર્યું હતું જેમાં જીન એમડલ મુખ્ય ઘડવૈયાઓ પૈકીના એક હતા. તે પ્રથમ કમર્શિયલ રીતે ઉપલબ્ધ કમ્પ્યુટર હતું જેમાં સંપૂર્ણ ઓટોમેટિક ફ્લોટિંગ પોઇન્ટ એરિથમેટિક કમાન્ડ્સનો ઉપયોગ થયો.[૪૪]

એપ્રિલ 1958માં એસ. ગિલ (ફેરન્ટી)એ સમાંતર પ્રોગ્રામિંગ વિશે અને શાખાકરણ (બ્રાન્ચિંગ) અને વેઇટિંગની આવશ્યકતા વિશે ચર્ચા કરી હતી.[૪૫] 1958માં જ આઇબીએમ (IBM)ના રિસર્ચર્સ જોન કોક અને ડેનિયલ સ્લોટનિકે પ્રથમ વખત આંકડાકીય ગણતરીઓ માટે સમાંતરણ વિશે ચર્ચા કરી હતી.[૪૬] બ્યુરોગ્સ કોર્પોરેશને 1962માં ડી825 રજૂ કર્યું હતું જે ચાર પ્રોસેસર ધરાવતું કમ્પ્યુટર હતું જેણે ક્રોસબાર સ્વિચ દ્વારા 16 મેમરી મોડ્યુલ્સ એક્સેસ કર્યા હતા.[૪૭] 1967માં એમડલ અને સ્લોટનિકે અમેરિકન ફેડરેશન ઓફ ઇન્ફર્મેશન પ્રોસેસિંગ સોસાયટીઝ કોન્ફરન્સ ખાતે સમાંતર પ્રોસેસિંગની સંભાવનાઓ વિશે ચર્ચાનું પ્રકાશન કર્યું હતું.[૪૬] આ ચર્ચા દરમિયાન સમાંતરણના કારણે સ્પીડ-અપની મર્યાદાને વ્યાખ્યાયિત કરવા માટે એમડલનો નિયમ રજૂ થયો હતો.

1969માં અમેરિકાની કંપની હનીવેલે તેની પ્રથમ મલ્ટિક્સ સિસ્ટમ રજૂ કરી હતી જે સિમેટ્રિક મલ્ટિપ્રોસેસર સિસ્ટમ હતી જે એક સાથે આઠ પ્રોસેસર્સને સમાંતરમાં ચાલુ કરી શકતી હતી.[૪૬] કાર્નેગી મેલોન યુનિવર્સિટી ખાતે 1970ના દાયકાનું એક મલ્ટિ-પ્રોસેસર પ્રોજેક્ટ સી.એમએમપી (C.mmp) “પ્રથમ મલ્ટિપ્રોસેસર્સ પૈકી એક હતું જેમાં અમુકથી વધારે પ્રોસેસર્સ હતા.”[૪૩] “સ્નૂપિંગ કેચિસ સાથે પ્રથમ બસ કનેક્ટેડ મલ્ટિ-પ્રોસેસર 1984માં સિનેપ્સ N+1 હતું.”[૪૩]

એસઆઇએમડી (SIMD) સમાંતર કમ્પ્યુટર્સની શરૂઆત 1970ના દાયકામાં થઇ હતી. પ્રારંભિક એસઆઇએમડી (SIMD) પાછળનો હેતુ મલ્ટિપલ સૂચનાઓ પર પ્રોસેસર્સના કન્ટ્રોલ યુનિટના ગેટ વિલંબને પુનઃ ભરપાઇ કરવાનો હતો.[૪૮] 1964માં સ્લોટનિકે લોરેન્સ લિવરમોર નેશનલ લેબોરેટરી માટે એક મેસિવલી (જંગી) સમાંતર કમ્પ્યુટર બનાવવાની દરખાસ્ત કરી હતી.[૪૬] તેની ડિઝાઇનને યુએસ એરફોર્સ દ્વારા ભંડોળ મળ્યું હતું જે સૌથી પ્રારંભનો એસઆઇએમડી (SIMD) સમાંતર કમ્પ્યુટિંગ પ્રયાસ આઇએલએલઆઇએસી IV (ILLIAC IV) હતો.[૪૬] તેની ડિઝાઇનની ચાવી અત્યંત ઊંચું સમાંતરણ હતું જે 256 પ્રોસેસર્સ સુધી હતું અને તે મશીનને જંગી ડેટાસેટ પર કામ કરવાની છુટ આપતું હતું જે પાછળથી વેક્ટર પ્રોસેસિંગ તરીકે ઓળખાયું. જોકે, આઇએલએલઆઇએસી IV (ILLIAC IV)ને “સૌથી કુખ્યાત સુપરકમ્પ્યુટર્સ” ગણવામાં આવ્યું હતું કારણ કે આ પ્રોજેક્ટ માત્ર ચોથા ભાગ સુધી પૂરો થયો હતો અને તેમાં 11 વર્ષ લાગી ગયા હતા અને પ્રારંભિક અંદાજ કરતા ચાર ગણો સમય લાગ્યો હતો.[૪૯] 1976માં તે પ્રથમ અસલ એપ્લિકેશન માટે ચાલુ થવા માટે અંતે તૈયાર હતું ત્યારે તે સમયે અસ્તિત્વ ધરાવતા ક્રે-1 જેવા કોમર્શિયલ સુપરકમ્પ્યુટર્સ કરતા તે પાછળ રહી ગયું હતું.

આ પણ જુઓ

[ફેરફાર કરો]- કન્કરન્ટ, સમાંતર અને ડિસ્ટ્રિબ્યુટેડ કમ્પ્યુટિંગમાં મહત્વના પ્રકાશનોની યાદી

- ડિસ્ટ્રિબ્યુટેડ કમ્પ્યુટિંગ પરિષદોની યાદી

- કન્ટેન્ટ એડ્રેસેબલ સમાંતર પ્રોસેસર

સંદર્ભો

[ફેરફાર કરો]- ↑ અલમાસી, જી. એસ. અને એ. ગોટલીબ (1989). હાઇલી પેરલલ કમ્પ્યુટિંગ . બેન્જામિન-ક્યુમિન્ગ્સ પબ્લિશર્સ, રેડવૂડ સિટી, કેલિફોર્નિયા

- ↑ એસ. વી. એડવી એટ અલ. નવેમ્બર 2008 "પેરલલ કમ્પ્યુટિંગ રિસર્ચ એટ ઇલિનોઇસ: ધ યુપીસીઆરસી (UPCRC) એજન્ડા" સંગ્રહિત ૨૦૦૮-૧૨-૦૯ ના રોજ વેબેક મશિન (પીડીએફ (PDF)). પેરલલ@Illinois, યુનિવર્સિટી ઓફ ઇલિનોઇસ, અર્બાના-કેમ્પેઇન ખાતે. “આ કામગીરી- વધેલી ક્લોક ફ્રિકવન્સી અને વધુ સ્માર્ટ પણ વધુ જટિલ આર્કિટેક્ચર-ના લાભો માટે મુખ્ય તકનિક હવે કથિત પાવર વોલ પર અથડાઇ રહી છે. કમ્પ્યુટર ઉદ્યોગે સ્વીકાર્યું છે કે કોરને ઝડપી બનાવવાના બદલે ભવિષ્યમાં એક જ કામગીરીમાં વૃદ્ધિ પ્રોસેસર્સ (અથવા કોર)ની વધતી સંખ્યા પરથી આવશે.”

- ↑ અસાનોવિક એટ અલ. ઓલ્ડ [કન્વેન્શનલ વિસડમ]: પાવર ઇસ ફ્રી, બટ ટ્રાન્ઝિસ્ટર્સ આર એક્સપેન્સિવ. ન્યૂ [કન્વેન્શનલ વિસડમ] ઇસ [ધેટ] પાવર ઇસ એક્સપેન્સિવ, બટ ટ્રાન્ઝિસ્ટર્સ આર "ફ્રી".

- ↑ અસાનોવિક, ક્રેસ્ટી એટ અલ. (ડિસેમ્બર 18, 2006). "“ધ લેન્ડસ્કેપ ઓફ પેરલલ કમ્પ્યુટિંગ રિસર્ચઃ એ વ્યૂ ફ્રોમ બર્કલી” (પીડીએફ (PDF)). યુનિવર્સિટી ઓફ કેલિફોર્નિયા, બર્કલી ટેકનિકલ રિપોર્ટ નં. UCB/EECS-2006-183. "ઓલ્ડ [કન્વેન્શનલ વિસડમ]: વધુ ક્લોક ફ્રિકવન્સી એ પ્રોસેસરની કામગીરી સુધારવાની પ્રાથમિક પદ્ધતિ છે. ન્યૂ [કન્વેન્શનલ વિસડમ]: વધુ સમાંતરણ પ્રોસેસરની કામગીરી સુધારવાની પ્રાથમિક પદ્ધતિ છે... ‘ઉંચી ક્લોક સ્પીડ વધુ સારી છે’ એવી માન્યતા સાથે સામાન્ય રીતે સંકળાયેલી કંપની ઇન્ટેલે પણ ચેતવણી આપી હતી કે ક્લોક સ્પીડ વધારીને કામગીરી મહત્તમ કરવાના પરંપરાગત વલણની મર્યાદા આવી ગઇ છે.”

- ↑ પેટરસન, ડેવિડ એ. અને જોહન એલ. હેનેસી (1998). કમ્પ્યુટર ઓર્ગેનાઇઝેશ એન્ડ ડિઝાઇન , બીજી આવૃત્તિ, મોર્ગન કૌફમન પબ્લિશર્સ, પાનું. 715. ISBN 1558604286.

- ↑ ૬.૦ ૬.૧ Barney, Blaise. "Introduction to Parallel Computing". Lawrence Livermore National Laboratory. મૂળ માંથી 2013-06-29 પર સંગ્રહિત. મેળવેલ 2007-11-09.

- ↑ હેનેસી, જોહન એલ. અને ડેવિડ એ. પેટરસન (2002). કમ્પ્યુટર આર્કિટેક્ચર: એ ક્વોન્ટિટેટિવ એપ્રોચ . ત્રીજી આવૃત્તિ, મોર્ગન કૌફમન, પાનું. 43. ISBN 1558607242.

- ↑ રાબે, જે. એમ. (1996). ડિજિટલ ઇન્ટિગ્રેટેડ સર્કિટ્સ . પ્રેન્ટિસ હોલ, પાનું. 235. ISBN 8125026568.

- ↑ ફ્લાયન, લૌરી જે."ઇન્ટેલ હોલ્ટ્સ ડેવલપમેન્ટ ઓફ ટુ ન્યૂ માઇક્રોપ્રોસેસર્સ". ધ ન્યૂ યોર્ક ટાઇમ્સ , મે 8, 2004. સુધારો, એપ્રિલ 22, 2008.

- ↑ Moore, Gordon E. (1965). "Cramming more components onto integrated circuits" (PDF). Electronics Magazine. પૃષ્ઠ 4. મૂળ (PDF) માંથી 2008-02-18 પર સંગ્રહિત. મેળવેલ 2006-11-11.

- ↑ એમડલ, જી. (એપ્રિલ 1967) "ધ વેલિડિટી ઓફ ધ સિંગલ પ્રોસેસર એપ્રોચ ટુ એચિવિંગ લાર્જસ્કેલ કમ્પ્યુટિંગ કેપેબિલિટીઝ". ઇન પ્રોસિડિંગ ઓફ એએફઆઇપીએસ (AFIPS) સ્પ્રિંગ જોઇન્ટ કમ્પ્યુટર કોન્ફરન્સ , એટલાન્ટિંગ સિટી, ન્યૂ જર્સી, એએફઆઇપીએસ (AFIPS) પ્રેસ, પાનાં 483–85.

- ↑ બ્રૂક્સ, ફ્રેડરિક પી. જુનિ. ધ માયથિકલ મન-મન્થ: એસે ઓન સોફ્ટવેર એન્જિનિયરિંગ . પ્રકરણ 2 – ધ માયથિકલ મેન મન્થ. ISBN 0201835959

- ↑ રિએવ્યુલેટિંગ એમડલ્સ લો સંગ્રહિત ૨૦૧૨-૦૬-૨૩ ના રોજ વેબેક મશિન (1988). કમ્યુનિકેશન્સ ઓફ ધ એસીએમ (ACM) 31(5), પાનાં 532–33.

- ↑ બર્નસ્ટીન, એ.જે. ((ઑકટોબર 1966) "પ્રોગ્રામ એનાલિસિસ ફોર પેરલલ પ્રોસેસિંગ,' આઇઇઇઇ (IEEE) ટ્રાન્સ ઓન ઇલેક્ટ્રોનિક કમ્પ્યુટર્સ". ઇસી-15, પાનાં 757–62.

- ↑ રૂસ્ટા, સૈયદ એચ. (2000). "પેરલલ પ્રોસેસિંગ એન્ડ પેરલલ અલગોરિથમ્સ: થિયરી એન્ડ કમ્પ્યુટેશન". સ્પ્રિન્ગર, પાનું 114. ISBN 0387987169.

- ↑ લામ્પોર્ટ, લેસલી (સપ્ટેમ્બર 1979). "હાઉ ટુ મેક એ મલ્ટિપ્રોસેસર કમ્પ્યુટર ધેટ કરેક્ટલી એક્ઝિક્યુટ્સ મલ્ટિપ્રોસેસ પ્રોગ્રામ્સ", આઇઇઇઇ (IEEE) ટ્રાન્ઝેક્શન્સ ઓન કમ્પ્યુટર્સ, સી-28,9, પાનાં 690–91.

- ↑ પેટરસન અને હેનેસી, પાનું 748.

- ↑ ક્યુલર, ડેવિડ ઇ.; જસવિન્દર પાલ સિંઘ અને અનૂપ ગુપ્તા (1999). પેરલલ કમ્પ્યુટર આર્કિટેક્ચર - એ હાર્ડવેર/સોફ્ટવેર એપ્રોચ . મોર્ગન કૌફમન પબ્લિશર્સ, પાનું 15. ISBN 1558603433.

- ↑ ક્યુલર એટ અલ. પાનું 15.

- ↑ પેટ, યાલે (એપ્રિલ 2004). "ધ માઇક્રોપ્રોસેસર ટેન યર્સ ફ્રોમ નાવ: વોટ આર ધ ચેલેન્જિસ, હાઉ ડુ વી મીટ ધેમ? (ડબલ્યુએમવી (WMV)). ડિસ્ટિંગ્યુશ્ડ લેક્ચરર ટોક એટ કાર્નેલી મેલન યુનિવર્સિટી. સુધારો 7 નવેમ્બર, 2007

- ↑ ૨૧.૦ ૨૧.૧ ક્યુલર એટ અલ. પાનું 124.

- ↑ ૨૨.૦ ૨૨.૧ ક્યુલર એટ અલ. પાનું 125.

- ↑ ૨૩.૦ ૨૩.૧ પેટરસન અને હેનેસી, પાનું 713.

- ↑ ૨૪.૦ ૨૪.૧ હેનેસી અને પેટરસન, પાનું 549.

- ↑ પેટરસન અને હેનેસી, પાનું 714.

- ↑ વોટ ઇસ ક્લસ્ટરિંગ? વેબોપિડીયા કમ્પ્યુટર ડિક્શનરી. સુધારો 7 નવેમ્બર, 2007.

- ↑ બીઓવુલ્ફ ડેફિનેશન. સંગ્રહિત ૨૦૧૨-૧૦-૧૦ ના રોજ વેબેક મશિન પીસી મેગેઝીન . સુધારો 7 નવેમ્બર, 2007.

- ↑ આર્કિટેક્ચર શેર ફોર 06/2007 સંગ્રહિત ૨૦૦૭-૧૧-૧૪ ના રોજ વેબેક મશિન. ટોપ500 (TOP500) સુપરકમ્પ્યુટિંગ સાઇટ્સ. ક્લસ્ટર્સ મેક અપ 74.60% ઓધ ધ મશિન ઓન ધ લિસ્ટ. સુધારો, 7 નવેમ્બર, 2007.

- ↑ હેનેસી અને પેટરસન, પાનું 537.

- ↑ એમપીપી (MPP) ડેફિનેશન. સંગ્રહિત ૨૦૧૩-૦૫-૧૧ ના રોજ વેબેક મશિન પીસી મેગેઝીન . સુધારો 7 નવેમ્બર, 2007.

- ↑ કર્કપેટ્રિક, સ્કોટ (જાન્યુઆરી 31, 2003). "કમ્પ્યુટર સાયન્સ: રફ ટાઇમ્સ અહેડ". સાયન્સ , વોલ્યૂમ. 299. નં. 5607, પાનાં 668 - 669. ડીઓઆઇ (DOI): 10.1126/સાયન્સ.1081623

- ↑ ૩૨.૦ ૩૨.૧ ૩૨.૨ ડી'એમર, માઇકલ આર. ચીફ ઓપરેટિંગ ઓફિસર, ડીઆરસી (DRC) કમ્પ્યુટર કોર્પોરેશન. "સ્ટાન્ડર્ડ રિકન્ફિગ્યુરેબલ કમ્પ્યુટિંગ". ઇનવાઇટેડ સ્પીકર એટ ધ યુનિવર્સિટી ઓફ ડેલવેર, ફેબ્રુઆરી 28, 2007.

- ↑ બોગન, શાકીયા અને ડેનીયલ એમ. પ્રેસલ (ઓગસ્ટ 2007). જીપીયુ (GPU): એન ઇમર્જીંગ પ્લેટફોર્મ ફોર જનરલ પરપઝ કમ્પ્યુટેશન સંગ્રહિત ૨૦૧૬-૧૨-૨૫ ના રોજ વેબેક મશિન (પીડીએફ (PDF)). એઆરએલ (ARL)-એસઆર (SR)-154, યુએસ આર્મી રિસર્ચ લેબ. સુધારો 7 નવેમ્બર, 2007.

- ↑ મસ્લેનિકોવ, ઓલેજ (2002). "સિસ્ટમેટિક જનરેશન ઓફ એક્ઝિક્યુટિંગ પ્રોગ્રામ ફોર પ્રોસેસર એલિમેન્ટ ઇન પેરલલ એએસઆઇસી (ASIC) ઓર એફપીજીએ (FPGA)-બેઝ્ડ સિસ્ટમ્સ એન્ડ ધેર ટ્રાન્સફોર્મેશન ઇનટુ વીએચડીએલ (VHDL)-ડિસ્ક્રિપ્શન ઓફ પ્રોસેસર એલિમેન્ટ કન્ટ્રોલ યુનિટ્સ". સંગ્રહિત ૨૦૨૦-૦૨-૧૧ ના રોજ વેબેક મશિન લેક્ચર નોટ્સ ઇન કમ્પ્યુટર સાયન્સ , 2328/2002: પાનું 272.

- ↑ શીમોકાવા, વાય.; વાય. ફુવા અને એન. અરામકી (18–21 નવેમ્બર 1991). એ પેરલલ એએસઆઇસી (ASIC) વીએલએસઆઇ (VLSI) ન્યૂરોકમ્પ્યુટર ફોર એ લાર્જ નંબર ઓફ ન્યુરોન્સ એન્ડ બિલિયન કનેક્શન્સ પર સેકન્ડ સ્પીડ. આઇઇઇઇ (IEEE) ઇન્ટરનેશનલ જોઇન્ટ કોન્ફરન્સ ઓન ન્યુરલ નેટવર્ક્સ. 3: પાનાં 2162–67.

- ↑ અકેન, કે.પી.; એમ.જે. ઇરવિન, આર.એમ. ઓવેન્સ (જુલાઇ 1998). "એ પેરલલ એએસઆઇસી (ASIC) આર્કિટેક્ચર ફોર એફિસિયન્ટ ફ્રેક્ટલ ઇમેજ કોડિંગ". સંગ્રહિત ૨૦૧૨-૧૦-૨૧ ના રોજ વેબેક મશિન ધ જર્નલ ઓફ વીએલએસઆઇ (VLSI) સિગ્નલ પ્રોસેસિંગ , 19 (2):97–113(17)

- ↑ કાહાન્ગ, એન્ડ્રુ બી. (જૂન 21, 2004) "સ્કોપિંગ ધ પ્રોબ્લેમ ઓફ ડીએફએમ (DFM) ઇન ધી સેમીકન્ડક્ટર ઇન્ડસ્ટ્રી સંગ્રહિત ૨૦૦૮-૦૧-૩૧ ના રોજ વેબેક મશિન." યુનિવર્સિટી ઓફ કેલિફોર્નિયા, સેન ડિયાગો. "ભવિષ્યની ડિઝાઇન ફોર મેન્યુફેક્ચરિંગ (ડીએફએમ (DFM)) ટેકનોલોજીએ ડિઝાઇન (બિન રિકવરીપાત્ર ખર્ચ) ખર્ચ ઘટાડવો જ જોઇએ અને સીધી રીતે ઉત્પાદન (બિન રિકવરીપાત્ર ખર્ચ) પર ધ્યાન આપવું જોઇએ.- માસ્ક સેટ અને પ્રોબ કાર્ડનો ખર્ચ – જે 90 એનએમ ટેકનોલોજી નોડ પર 1 મિલિયન ડોલરથી વધુ છે અને સેમીકન્ડક્ટર આધારિત સંશોધન પર મોટો અવરોધ પેદા કરે છે."

- ↑ ૩૮.૦ ૩૮.૧ પેટરસન અને હેનેસી, પાનું. 751.

- ↑ ધ સિડની ફર્નબાક ઓવોર્ડ ગિવન ટુ એમપીઆઇ (MPI) ઇન્વેન્ટર બિલ ગ્રૂપ સંગ્રહિત ૨૦૧૧-૦૭-૨૫ ના રોજ વેબેક મશિન રિફર્સ ટુ એમપીઆઇ (MPI) એઝ "ધ ડોમિનન્ટ એચપીસી (HPC) કમ્યુનિકેશન્સ ઇન્ટરફેસ"

- ↑ શેન, જોન પોલ અને મિકો એચ. લિપાસ્ટી (2005). મોડર્ન પ્રોસેસર ડિઝાઇનઃ ફંડામેન્ટલ્સ ઓફ સુપરસ્કેલર પ્રોસેસર્સ . મેકગ્રો-હિલ પ્રોફેશનલ. પાનું 561. ISBN 0070570647. "જોકે, આવા રિસર્ચની સૌથી મહત્વની બાજુ- સિરિયલ પ્રોગ્રામ્સનું ઓટોમેટેડ સમાંતરણ – હજુ અમલમાં આવ્યું નથી. જોકે, વિવિધ વર્ગના એલ્ગોરિધમ્સના ઓટોમેટેડ સમાંતરણનું પ્રદર્શન થયું છે, ત્યારે આવી સફળતા મોટા ભાગે વૈજ્ઞાનિક અને આંકડાકીય એપ્લિકેશન્સ પૂરતી મર્યાદિત છે જ્યાં આગાહી કરી શકાય તેવો ફ્લો કન્ટ્રોલ (જેમ કે સ્ટેટિકલી નક્કી કરાતા ઇટરેશન કાઉન્ટ સાથે નેસ્ટેડ લૂપ સ્ટ્રક્ચર્સ) અને સ્ટેટિકલી એનાલાઇઝેબલ મેમરી એક્સેસ પેટર્ન. (જેમ કે ફ્લોટ પોઇન્ટ ડેટા પર વિશાળ બહુપરિમાણિય સંગ્રહ પર)”

- ↑ અસાનોવિક, ક્રસ્ટે, એટ અલ. ડિસેમ્બર 18, 2006 લેન્ડસ્કેપ ઓફ પેરલલ કમ્પ્યુટિંગ રિસર્ચ: એ વ્યૂ ફ્રોમ બર્કલી (પીડીએફ (PDF)). યુનિવર્સિટી ઓફ કેલિફોર્નિયા, બર્કલી. ટેકનિકલ રિપોર્ટ નં. UCB/EECS-2006-183. જુઓ ટેબલ 17–19 પાના પર

- ↑ મેનાબ્રીએ, એલ. એફ. (1842). સ્કેચ ઓફ ધ એનાલિટિક એન્જિન ઇન્વેન્ટેડ બાય ચાર્લ્સ બેબેજ. બાઇલિયોથિક યુનિવર્સિલી દી જીનીવા. સુધારો નવેમ્બર 7, 2007

- ↑ ૪૩.૦ ૪૩.૧ ૪૩.૨ પેટરસન અને હેનેસી, પાનું. 753.

- ↑ da Cruz, Frank (2003). "Columbia University Computing History: The IBM 704". Columbia University. મેળવેલ 2008-01-08.

- ↑ પેરલલ પ્રોગ્રામિંગ, એસ. ગિલ, ધ કમ્પ્યુટર જર્નલ વોલ્યૂમ. 1 #1, પાના 2-10, બ્રિટીશ કમ્પ્યુટર સોસાયટી, એપ્રિલ 1958.

- ↑ ૪૬.૦ ૪૬.૧ ૪૬.૨ ૪૬.૩ ૪૬.૪ Wilson, Gregory V (1994). "The History of the Development of Parallel Computing". Virginia Tech/Norfolk State University, Interactive Learning with a Digital Library in Computer Science. મેળવેલ 2008-01-08.

- ↑ Anthes, Gry (November 19, 2001). "The Power of Parallelism". Computerworld. મૂળ માંથી 2008-01-31 પર સંગ્રહિત. મેળવેલ 2008-01-08.

- ↑ પેટરસન અને હેનેસી, પાનું 749.

- ↑ પેટરસન અને હેનેસી, પાના 749–50: પાછળના પ્રોજેક્ટ્સમાં કેટલીક ટેકનોલોજી લાગુ પાડવા માટે સફળ રહેવા છતાં આઇએલએલઆઇએસી IV (ILLIAC IV) કમ્પ્યુટર તરીકે નિષ્ફળ ગયું. આયોજિત મશીનનો માત્ર ચોથો ભાગ તૈયાર થયો હોવા છતાં 1966માં ખર્ચ 8 મિલિયન ડોલરથી વધીને 1972માં 31 મિલિયન ડોલર સુધી પહોંચ્યો હતો... તે કદાચ સૌથી કુખ્યાત સુપરકમ્પ્યુટર હતું. આ પ્રોજેક્ટ 1965માં શરૂ થયો હતો અને તેનું પ્રથમ વાસ્તવિક એપ્લિકેશન 1976માં ચાલુ કર્યું હતું."

વધુ વાંચન

[ફેરફાર કરો]- સી. રોડરિગ્ઝ, એમ. વિલેગ્રા એન્ડ બી. બેરન,ઢાંચો:Doi-inline બાયોનેટિક્સ 2007, પાનાં 66–69, 2007.

બાહ્ય લિંક્સ

[ફેરફાર કરો]- સમાંતર કમ્પ્યુટિંગ at the Open Directory Project

- લોરેન્સ લિવરમોર નેશનલ લેબોરેટરીઃ સમાંતર કમ્પ્યુટિંગનો પરિચયસંગ્રહિત ૨૦૧૩-૦૬-૧૦ ના રોજ વેબેક મશિન

- સમાંતર પ્રોગ્રામ્સનું ડિઝાઇનિંગ અને નિર્માણ, ઇયાન ફોસ્ટર દ્વારા

- ઇન્ટરનેટ સમાંતર કમ્પ્યુટિંગ આર્કાઇવ સંગ્રહિત ૨૦૦૨-૧૦-૧૨ ના રોજ વેબેક મશિન

- આઇઇઇઇ (IEEE) ડિસ્ટ્રીબ્યુટેડ કમ્પ્યુટિંગ ઓનલાઇન ખાતે સમાંતર પ્રોસેસિંગ ટોપિક એરિયા સંગ્રહિત ૨૦૧૧-૦૯-૨૮ ના રોજ વેબેક મશિન

- સમાંતર કમ્પ્યુટિંગ વર્ક્સ ફ્રી ઓનલાઇન બુક સંગ્રહિત ૨૦૧૧-૦૭-૨૭ ના રોજ વેબેક મશિન

- ફ્રન્ટલાઇન્સ ઓફ સુપરકમ્પ્યુટિંગ ફ્રી ઓનલાઇન બુક જેમાં એલ્ગોરિધમ્સ અને ઔદ્યોગિક એપ્લિકેશન્સ જેવા વિષયો આવરી લેવાયા છે

- વૈશ્વિક સમાંતર કમ્પ્યુટિંગ સંશોધન કેન્દ્ર સંગ્રહિત ૨૦૦૮-૧૦-૨૦ ના રોજ વેબેક મશિન

- કોલંબિયા યુનિવર્સિટી ખાતે સમાંતર કમ્પ્યુટિંગના અભ્યાસક્રમો (આઇબીએમ ટી. જે. વોટ્સન એક્સ10 પ્રોજેક્ટના સહયોગથી સંગ્રહિત ૨૦૧૦-૦૧-૨૨ ના રોજ વેબેક મશિન